How hardware emulation helps drones take flight

I recently had the chance to visit with Bo Shen, founder and CTO of Artosyn Microelectronics. The fabless Shanghai-based company, established in 2011, specializes in SoCs for one of today’s most exciting markets: drones.

Bo shared details of both Artosyn’s latest designs and the verification flow the company has needed to adopt to realize an SoC that can power these increasingly autonomous and influential products.

Before diving into our conversation let’s look at why drones are growing in importance and complexity. We need a sense of where the challenges facing Bo and his team come from.

Tesla… but for drones

In the 1898 patent, “Method of and Apparatus for Controlling Mechanism of Moving Vessels or Vehicles”, Austrian inventor Nikola Tesla described the wide range of possibilities for his new radio-control technology:

“The invention which I have described will prove useful in many ways. Vessels or vehicles of any suitable kind may be used to dispatch, or pilot boats or the like, or for carrying letters, packages, provisions, instruments, objects… but the greatest value of my invention will result from its effect upon warfare and armaments, for by reason of its certain and unlimited destructiveness it will tend to bring about and maintain permanent peace among nations.”

Tesla’s prophecy turned out to be mostly true, if not for the questionable closing statement. Permanent peace among nations? Not today. He was certainly correct in anticipating today’s multitude of applications for commercial unmanned aerial vehicle (UAV) or drones.

In less than a decade, commercial drones have evolved from remote-controlled toys with a limited flying range and few capabilities into professional tools boasting advanced features and skills. Drones are routinely used in many different fields, such as delivery vehicles (Amazon), aerial imaging, photo and video, augmented reality games, supervising conservation efforts in remote locations, fertilizing crop fields, monitoring traffic incidents, surveying hard-to-reach places and facilitating research projects. The growing market for civilian drones is having an impact on a variety of industries, including real estate, media, film & TV production, construction, mining, agriculture, utilities, private security and law enforcement.

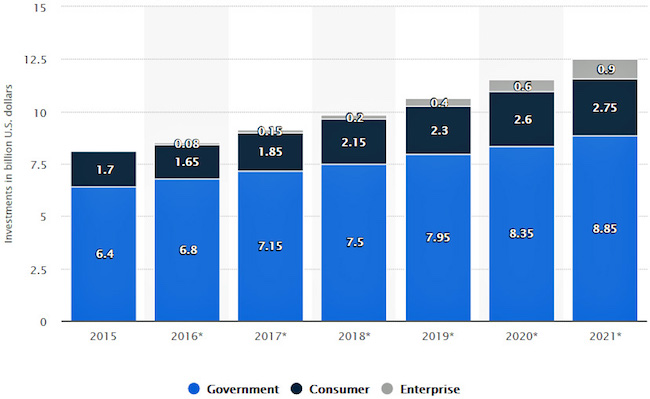

According to BI Intelligence, the civilian drone market is expected to grow at a compound annual growth rate (CAGR) of 19% by 2020 versus 5% for the military market (Figure 1).

The fast progress has been made possible by a powerful system-on-chip (SoC) design at the heart of any high-end drone. The embedded design controls the navigation of the device. Over time, it has reached a level of sophistication that makes drones fully automatic flying objects. Such drones could soon automate everyday tasks such as fertilizing crop fields, monitoring traffic incidents, surveying hard-to-reach places, and much more. Drones with advanced capabilities are the vehicles of the future. In not too distant future, people will find it almost impossible to imagine life without them.

But to do all that, we need companies like Artosyn to deliver the silicon.

A conversation with Bo Shen

Lauro: It is nice talking to you Bo. Would you please share with us a bit of background about you and Artosyn?

Bo: With great pleasure. I founded Artosyn in 2011. Back then, the drone market was in its infancy, but I strongly believed that it would soon take off and grow at a steep rate. Which is exactly what happened. My goal was to design chips for the drone market.

Since 2012, Artosyn has developed various chipsets as flight controllers for commercial drones. Today, Artosyn is a well-known player in the drone industry. Our designs power commercial drones from DJI and others.

In 2015, I started to design a new generation of controllers that make use of artificial intelligence (AI), useful for tasks such as object detection, object classification, object tracking, etc. These new chips can be use in a wide range of applications, in the drone, surveillance, and advanced driver assistance systems (ADAS) markets.

Lauro: Please, briefly describe the controller.

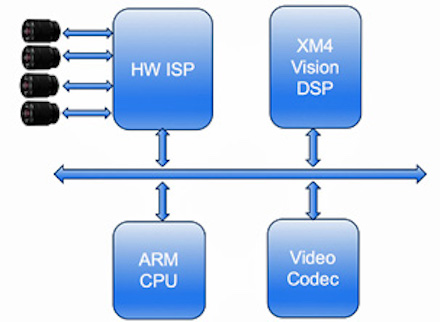

Bo: The controller has a complexity of about 100 million ASIC-equivalent gates, plus about 70Mbit of memory. The fabric encompasses two ARM Quad-cores CPUs [Cortex A7], a vision DSP [Quad CEVA XM4 DSP], and several peripherals such as DDR3/4, MIPI PHY, HDMI PHY, USB3.0, PCIe-2.0 and others. The design is devised to consume low power in the order of 10 Watts.

The SoC is managed by two operating systems, a Linux OS and a freeRTOS, with a total amount of code around one million lines. The freeRTOS is used for tasks that need real-time processing, while Linux is used for file system management and the Ethernet/USB/PCIE driver (Figure 2 shows a block diagram of the SoC).

Figure 2. The block diagram of the Artosyn SoC Drone Controller illustrates its easy customization (Artosyn).

The SoC has been designed to allow for easy customization to accelerate the adoption of drones in several industries.

Lauro: What are some of the most pressing challenges you face in verifying your design?

Bo: The design is processing a vast amount of data, essential for applying AI to extract vital flight information. The artificial intelligence SoC is the most complex chip ever designed at Artosyn, and its verification is the most challenging task. The SoC integrates various high-speed interfaces, such as USB3.0, DDR3/4 PHY, MIPI and HDMI receiver, which are difficult to verify with RTL simulation or FPGA prototyping.

In our previous projects, we used FPGA prototyping, but it was rather difficult to find the root cause of design bugs on FPGAs. Poor design visibility and long compilation time stretch design-iterations to trace a single bug into weeks. To overcome such drawbacks, we chose Mentor’s Veloce emulation system for this project. Today, we use Veloce to find most of the hardware and OS bugs, and then use FPGA prototyping for software application development for its higher running speed.

Lauro: Briefly describe your verification flow.

Bo: We verify our SoC in three steps:

- Step 1: Block-level verification via RTL simulation

- Step 2: Block/chip level verification and hardware/software integration using Veloce hardware emulation

- Step 3: Software application development and block testing that needs real time verification via FPGA prototyping

The first benefit we get from Veloce is its acceleration factor of 1,000x over RTL simulation. Secondly, the VirtuaLAB feature of Veloce solves the verification challenge of high-speed interfaces, such as USB3.0, DDR PHY and PCIe.

We use Veloce in a combination of modes. Transaction-based verification and standalone emulation can meet most of our requirements. In-circuit emulation [ICE] enables us to connect the design to real-world interfaces – such as USB and PCIe – and exercise the design via real traffic to further improve the verification coverage and enhance our confidence on the verification quality.

We have been using Veloce for about one year. Today, 25 engineers have access and use it every day. Hardware engineers use Veloce for block-level verification and chip-level regression testing. Software engineers use it for OS booting and driver/firmware development.

Lauro: What kinds of problems have you been able to identify using Veloce?

Bo: Because of its high speed of execution compared to software simulation, Veloce can find bugs in RTL code quickly, which may need weeks of software simulation. For example, to process one video frame in a 4K HEVC video codec embedded in the design, the simulator needs one full day, but Veloce takes only minutes to do the same job.

Lauro: What business benefits have you realized by using Veloce?

Bo: Our verification productivity has been greatly improved, for both hardware and software design –– in the ballpark of 3X. In addition, design verification is more complete, achieving an even higher level of product quality, and ultimately reducing the risk of chip respins.

Lauro: How many weeks/months did Veloce save you in releasing a verified design?

Bo: With Veloce, we have been able to reduce the chip design cycle by more than six months.

Lauro: This is a remarkable result. In closing, can you mention any enhancement to Veloce that you would like Mentor to address in the future?

Bo: For software engineers responsible for OS porting, it may take long time to wait for OS booting. We would like to see higher execution speed for software development.

Lauro: Bo, thank you for taking the time to talk to me today. You provided a treasure trove of interesting information.

Dr Lauro Rizzatti is a verification consultant and industry expert on hardware emulation. He holds a doctorate in Electronic Engineering from the Universita` degli Studi di Trieste in Italy and presently divides his time between the US and Europe.

Dr Lauro Rizzatti is a verification consultant and industry expert on hardware emulation. He holds a doctorate in Electronic Engineering from the Universita` degli Studi di Trieste in Italy and presently divides his time between the US and Europe.