April 10, 2013

It’s time to take up the challenge of applying 3D integration technology to IC design. The manufacturing process technology is maturing, the tool chains are in place, and the opportunities to broaden your market by applying a new form of systemic integration are growing.

April 10, 2013

An increasingly important concept in design is that of product creation. An approach based on product creation looks beyond chip or board design.

April 9, 2013

The chipmaker used Calypto’s PowerPro to carry out power analysis of its latest core design at the RTL rather than at post-gate synthesis.

April 4, 2013

Debug of logic and testbench debug makes up 35% of chip design, and is growing as power-management and hardware/software issues become part of the task.

April 1, 2013

You can waive some physical verification errors related to legacy IP found in foundry DRC checks. Knowing which has involved lengthy manual analysis. TSMC is enhancing the process with automation.

March 11, 2013

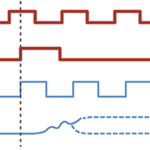

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

February 12, 2013

Now companies in any tier can use development kits as a platform to speed development, bridge the hardware-software divide and build out ecosystems quickly.

February 12, 2013

The technique drove ‘agile systems development’ for the programmable logic vendor’s new product line.

February 5, 2013

Cache coherency implemented in hardware increases the verification effort. VIP-based strategies are described with particular reference to ARM protocols.

January 31, 2013

Trying to balance your use of simulation and FPGA prototyping is tough. Acceleration used with Accelerated VIP offers simulation-like visibility and debug with near FPGA performance.