August 15, 2019

Hierarchical DFT for Arm-based SoCs is easier than ever with the arrival of a complete reference flow from Mentor and Arm.

August 9, 2019

Doc Formal rounds up some of the the key observations about verfication made during July’s Synopsys VC Formal SIG event in India.

July 27, 2019

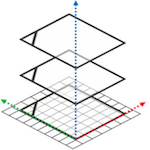

Whether you use OASIS or GDSII, unwanted duplicate cells can make their way into the final SoC database. Learn how to remove them.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

July 4, 2019

Doc Formal describes a strategy developed by his company Axiomise to apply formal verification proofs to open-source processor for safety, security and reliability.

June 18, 2019

Integrated design environments and features within them such as auto-complete deliver valuable efficiencies for input, verification and debut.

June 11, 2019

How to remove or extract portions of a layout for easier, more focused and faster project delivery.

May 21, 2019

How Mentor develops and works with partners to prepare each version of its Calibre DFM platform to be ready for the introduction of each new process node.

May 15, 2019

Text editors have major debug limitations that the use of hyperlinks in integrated development environments help you overcome.

May 14, 2019

Part two of this feature describes three use-cases that exploit the VirtuaLAB technology in HDMI, PCIe and Ethernet designs.