October 8, 2013

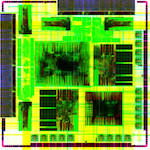

Electrically aware layout tools provide a more efficient alternative to time-consuming rip-up-and-retry practices in mixed-signal nanometer IC design.

October 7, 2013

Build tools around the dataflows and control systems engineers model to address verification challenges posed by burgeoning complexity and low power.

October 2, 2013

New layout-dependent effects (LDEs) arise at each process node. This methodology updates LDE parameters and uses on-the-fly simulation for early detection.

September 24, 2013

How the HPC company used Synopsys' Lynx Design System to standardise its flow and simplify migration to the next node.

September 17, 2013

Power intent, signal isolation and level shifting can all be controlled in a UPF-based multi-voltage IC design through careful coding.

September 3, 2013

This article looks at the way in which various representations of a block of a design have different implications in a UPF based power-aware hierarchical design flow.

August 12, 2013

3D-IC design is ready for take-off, following several years of intense collaboration to develop the necessary tools, methodologies and flows

July 31, 2013

How the company migrated to an OVM-based methodology to design and verify a 30 million-gate ASIC design, on the path to UVM.

July 19, 2013

How Cisco eliminated iterations in the ASIC handoff of a gigahertz networking chip by using physically aware synthesis

May 29, 2013

How to design with finFETs, including the impact on standard cells, IP, SRAM; the effects of fin quantization; extraction and parasitics; AMS issues and more.