July 26, 2012

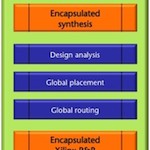

How Cadence, Intel and Xuropa accelerated the semiconductor design process by squeezing 15% more capacity out of a virtualized server farm

July 5, 2012

Using a new design-partitioning tool and stacked-silicon interconnect FPGA to develop an ASIC prototyping platform that can be reprogrammed several times a day.

May 21, 2012

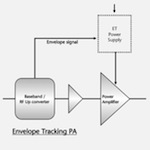

Current techniques for modelling RF power amplifiers don't provide the dynamic range necessary to simulate their performance properly when used in the energy-saving envelope-tracking mode necessary to give LTE terminals a decent battery life.

March 21, 2012

Texas Instruments’ MSP430 microcontroller platform has been one of the industry’s leading ultra-low-power architectures for more than a decade. Each generation has been focused on setting new records. The latest, Wolverine, cuts power and energy consumption by more than half.

March 7, 2012

‘Envelope tracking’ is not a new technique; it has been known about for more than 50 years. But it could greatly help the power consumption challenges once more facing mobile handset design.

January 23, 2012

There’s already some love out there for ARM’s v8 64bit architecture as the processor giant builds out its ecosystem.

August 23, 2011

By the time a serious lithography-related problem is identified at the fab, it is too late in the design process to make simple layout changes. To avoid or reduce design delays, Infineon Technologies uses lithography simulation to detect weak points in a layout and analyze the effect of lithography on the design’s electrical performance. Its [...]

August 23, 2011

This article describes various non-volatile memory (NVM) intellectual property (IP) alternatives with specific reference to their integration within system-on-chip designs targeting the 65nm process node and below. The article considers many of the strengths and vulnerabilities of these IP options, and then describes the tests that must be undertaken to ensure their long-term reliability, particularly [...]

August 23, 2011

Intel says ‘trigate’—finFET to others—but depleted silicon-on-insulator also has its post 22nm supporters. Chris Edwards reports on the debate at 2011’s Semicon West.

July 14, 2011

The QorIQ AMP (Advanced Multi-Processing) family was unveiled by Freescale Semiconductor in June and is an aggressive play for the control plane market. As such it is both innovative in its own right and also shows what kind of performance communications designers must deliver to meet the overall system demands of today’s customers. At its […]