FPGA playing verification catch-up as bugs escape

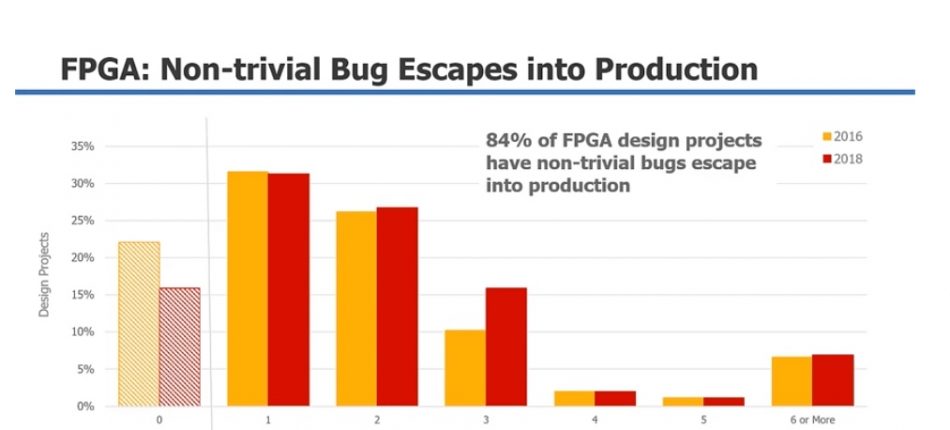

Some 84% of FPGA-based design projects have non-trivial bugs that escape into production, according to the 2018 Wilson Research Group ASIC and FPGA functional verification study.

The biennial Mentor-commissioned study started tracking these bug escapes in 2016 to provide a comparison with the respin rate for ASICs and measure the maturity of verification processes for the different design targets (Figure 1).

Introducing the 2018 results, Harry Foster, Chief Scientist, Verification at Mentor, noted that the FPGA market is maturing its verification processes, but still has some way to go.

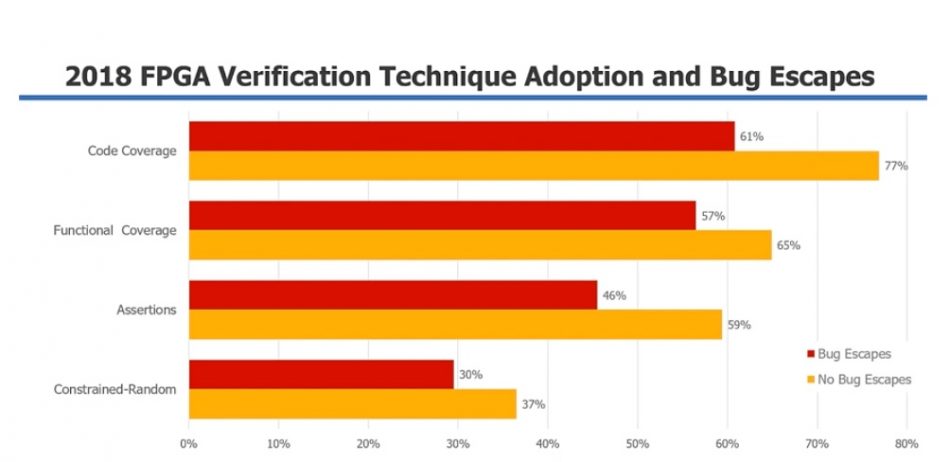

For those projects that had no bug escapes, there was a consistently higher adoption of verification techniques such as code coverage, functional coverage, assertions and constrained-random strategies (Figure 2).

Figure 2. Projects with no bug escapes have generally adopted more advanced verification techniques (Wilson Research Group/Mentor)

Some sense of how FPGA verification methodologies are have to play catch-up relative to those for ASIC design can also be seen in the comparative growth rate in the use of static techniques. Formal property checking now has a 20.75% CAGR for adoption across FPGA projects, compared with 5.3% in the more mature ASIC sector.

Another notable finding was that the number of ASIC projects achieving first silicon success has slipped to 26% having been consistently at around 30% across the last three studies.

Design complexity appears to be playing a role here, but teams are also having to deal with a greater volume of requirements for safety and security and the challenges posed by hardware/software interactions.

The ratio of design to verification engineers across projects of all sizes is now roughly 1:1 (e.g, 4.6 design/5.0 verification for FPGAs). In addition, design engineers spend around 45% of their time also working on verification tasks (46% for ASIC; 44% for FPGA).

The Wilson study’s findings were released last week and a full online presentation is now available to view on-demand. The study and presentation also consider issues such as delivery schedules and the types of flaws that typically cause respins.