May 3, 2021

Learn how power-intent, LDEs, ESD and voltage-aware spacing techniques can particularly benefit from the use of static verification checks.

October 16, 2019

Power intent files have increased efficiency and the use of an IDE can prevent them becoming outdated as a design evolves.

November 23, 2014

Emulation and simulation acceleration technologies provide the means to more efficiently detect power issues before tapeout – and find the worst-case modes that need to be fixed.

September 17, 2013

Power intent, signal isolation and level shifting can all be controlled in a UPF-based multi-voltage IC design through careful coding.

September 3, 2013

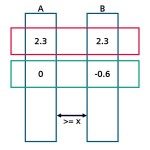

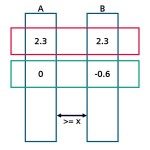

This article looks at the way in which various representations of a block of a design have different implications in a UPF based power-aware hierarchical design flow.

July 25, 2013

Formal verification techniques are becoming more widely used as the size and complexity of SoCs and increases.