Sonics readies fine-grained power-gating architecture

On-chip networks specialist Sonics is extending into power management with an approach intended to substantially automate much of the job of building finely grained power-gated SoCs.

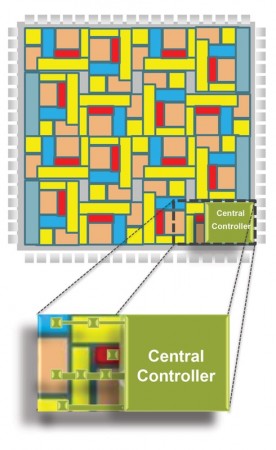

The ICE-Grain approach developed by the company is intended to make it possible to divide the SoC into power-gated ‘grains’ that can be an order of magnitude smaller than those used by many designs. Each grain is connected to one or more clock domains and attached to at least one power domain, with the ability to group grains into a larger hierarchy.

Grains are connected to central and local control circuitry blocks that are synthesized by tools developed for the architecture and which deliver runtime control over power. The centralized grain controller block manages power sequencing and operating point assignment. The local controller blocks in each grain handle power sequence execution and are designed to minimize the logic in the always-on domain.

Sonics claims the approach it has taken will let designers exploit many more power-down states across the chip than they can typically achieve using primarily software-controlled approaches. The architecture supports “wake on demand” to allow instantaneous wake up of grains when they are needed by logic in other grains.

Power control automation

Drew Wingard, CTO of Sonics, said: “Our goal with the ICE-Grain power architecture is to give system architects the IP, drivers, and automation tools they need to address power reduction early in the SoC design process where it proves most effective.

“To save power, designers must power-down parts of the SoC as quickly as possible to eliminate leakage current, and then power the parts back up just in time. Our fine-grain approach controls power in hardware for much faster switching between states. This approach also implements dynamic voltage and frequency scaling to take advantage of the high dependence of active power on voltage.”

Image A central power controller communicates with local agents in each grain

Designers will need to determine how best to split the design into grains that can best take advantage of power gating and voltage scaling, although the adoption of an architecture built for automation could yield tools to help, said Wingard. “Determining appropriate power grain partitioning is certainly an important task. I think the biggest challenge in this area is the lack of good modeling tools to help architects and integration teams make the partitioning choices.

“While a number of small EDA companies have tried to make a business in this area, I believe that their success has been limited because of the small number of SoC teams pursuing aggressive dynamic power management. It is my expectation that the introduction of ICE-Grain will substantially grow the market for such tools. Sonics is very interested in participating together with EDA vendors and customers to drive significant improvements in these modeling technologies.”

UPF adoption driver

Wingard said the improving automation of low-power design will help with implementation of the ICE-Grain architecture: “One of the reasons that we held off the introduction of this technology for several years was the immaturity of the rest of the implementation flows around topics like electrical and logical rules and verification.

“The industry’s adoption of the IEEE 1801 UPF standard has provided a stable physical implementation platform that enables technologies like ICE-Grain to be safely implemented.”

Rich Wawryzniak, senior market analyst at Semico Research, said: “There is a large market opportunity for an IP supplier that delivers a commercial solution on par with the most advanced power schemes developed by the ‘army of experts’ at large system companies like Apple. We believe there is strong pent-up demand for an automated power management solution with chip design teams building mainstream products in more modest volumes than Apple.”