September 7, 2020

But you were NOT afraid to ask.... It's time for some answers.

May 29, 2020

Virtualization is becoming ever more common during the Covid-19 outbreak, even for complex technologies like emulation, and showing its strengths.

September 18, 2019

A look at the complexiites of implementing a Bluetooth Low Eenergy interface in an SoC.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

September 13, 2019

A look at the device types defined by the Compute Express Link (CXL) standard.

September 12, 2019

A look at the key protocols that control the Compute Express Link (CXL) standard for connecting CPUs and accelerators in hetereogenous computing environments.

September 11, 2019

A guide to the emerging Compute Express Link (CXL) standard, which links CPUs and accelerators in heterogenous computing environments.

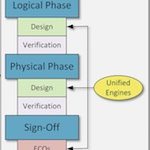

September 9, 2019

Complex SoCs need systemic optimisation to achieve best time to results, enabled by the use of a unified RTL-to-GDSII flow underpinned by a unified data model.

September 3, 2019

Using a hardware root of trust and a secure development lifecycle process to form the basis of a better approach to developing and implementing more secure complex SoCs.

August 9, 2019

Doc Formal rounds up some of the the key observations about verfication made during July’s Synopsys VC Formal SIG event in India.