April 1, 2013

You can waive some physical verification errors related to legacy IP found in foundry DRC checks. Knowing which has involved lengthy manual analysis. TSMC is enhancing the process with automation.

March 11, 2013

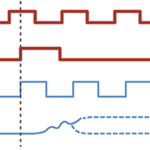

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

February 5, 2013

Cache coherency implemented in hardware increases the verification effort. VIP-based strategies are described with particular reference to ARM protocols.

January 31, 2013

Trying to balance your use of simulation and FPGA prototyping is tough. Acceleration used with Accelerated VIP offers simulation-like visibility and debug with near FPGA performance.

January 24, 2013

How should you quiz your verification IP vendor to get the right VIP for your needs? Synopsys' Neill Mullinger details a checklist of the key points to raise.

January 23, 2013

Real-valued modelling provides a way of speeding up the simulation of SoCs with significant analog content through the use of discrete-event solvers.

November 16, 2012

The business case behind how virtual prototyping speeds development, improves hardware and software quality, and improves ROI.

October 30, 2012

An exclusive extract from Cadence Design Systems' Mixed-Signal Methodology Guide provides an excellent overview of its discrete topic and a flavor of the book as a whole.

October 26, 2012

Overcome the time and visibility limitations of simulation and of gate-level and RTL-based strategies to achieve full-chip analysis.

October 3, 2012

The technique enables early software development and hardware/software co-design strategies before a project is more rigidly defined in RTL.