April 5, 2012

More than half of design companies claim to use ABV but many have yet to deploy full methodologies.

April 5, 2012

Building a prototype SoC in one or a set of FPGAs can aid field trials, software development and hardware/software integration. But it's not easy, so the decision to go ahead needs careful consideration.

March 28, 2012

Verification IP is becoming an increasingly important component for system design due to the rapid proliferation of new protocols and interfaces, chiefly driven by mobile comms.

March 20, 2012

Logic glitches in asynchronous clock domain crossing paths can arise even when synthesis tools declare a design’s RTL and gate-level netlists equivalent. This article describes Real Intent’s approach to capturing them.

March 19, 2012

Root-cause analysis of detected errors is a key design step. Debugging can take more than half of the verification effort. Vennsa’s OnPoint automated debug technology has been integrated with Springsoft’s Verdi visualization platform to reduce cost and uncertainty.

March 7, 2012

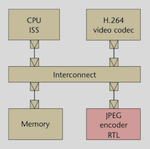

An evolved ESL-to-RTL methodology flow addresses the ‘discipline gaps’ between software and hardware engineering by using three system level-based software-hardware verification steps. The strategy is already available in TSMC’s Reference Flow 12.

February 28, 2012

This two-part article discusses the verification requirements of the RTCA DO-254 design assurance guidelines, including advanced methods for use on class DAL A/B designs. The first part provides a general overview. It also explains the original intent behind the concept of 'elemental analysis', how it is typically satisfied today with code coverage, and the limitations [...]

January 24, 2012

Functional logic errors remain a significant cause of project delays and re-spins. One of the main reasons is that two important aspects of verification environment quality—the ability to propagate the effect of a bug to an observable point and the ability to observe the faulty effect and thus detect the bug—cannot be analyzed or measured. [...]

August 23, 2011

The article describes a novel optimization approach that extends leading methodologies to improve performance, power and area. It is based on a pre-generated cell library that extends commercially available foundry libraries and couples it with novel logic optimization to aim for the delivery of near full-custom performance levels. The approach assesses the gate-level netlist generated [...]

August 23, 2011

Bridging the analog-digital divide is tough, particularly when it comes to verification. The two domains are marked by a host of differences with regard to tools, methodologies and the basic means of developing and testing designs. Analog engineers do most of their work by building and moving graphics while their digital counterparts do most of [...]