July 3, 2014

How Wall Street's vastly resourced IT teams already point the way to cheaper, faster and more efficient verification by putting goals not tools first.

April 16, 2014

Performing clock-domain crossing (CDC) checks on a flat database is difficult on complex SoCs. Hierarchy improves speed but calls for a smarter approach.

January 27, 2014

Find how to spot some of the most common false clock-domain crossing (CDC) violations and how to efficiently find actual CDC problems that could kill a design if not corrected.

July 25, 2013

Formal verification techniques are becoming more widely used as the size and complexity of SoCs and increases.

July 3, 2013

Clock domain crossing bugs undermine the productivity gains of moving to block-based design, but can be tackled through hierarchical formal analysis.

May 14, 2013

RTL sign-off strategies ease SoC design and IP integration by enabling early analysis and optimization of CDC, power, X propagation, timing, and resetability issues.

May 7, 2013

Better upfront analysis can help avoid propagating errors from RTL into the netlist, and reveal a number of ways to improve the quality of your final design.

March 11, 2013

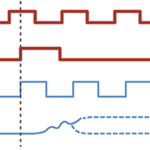

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

March 20, 2012

Logic glitches in asynchronous clock domain crossing paths can arise even when synthesis tools declare a design’s RTL and gate-level netlists equivalent. This article describes Real Intent’s approach to capturing them.

January 24, 2012

The inherent complexity of today’s system-on-chips, with their multiple clock and voltage domains, requires test considerations to be moved further up design flows. The article describes strategies for and benefits from apply test before RTL goes through synthesis, augmenting what is already achieved through memory built-in self test and automatic test pattern generation.