Siemens automates test to handle multi-die 2.5D, 3D and 5.5D architectures

Siemens has introduced Tessent Multi-die, design-for-test (DFT) software that targets the particular challenges posed by emerging and increasingly mainstream silicon architectures and structures.

Interposers, stacked die and now stacked die on interposers. Integration is moving along a path through, respectively, 2.5D, 3D toward what are now being called 5.5D architectures.

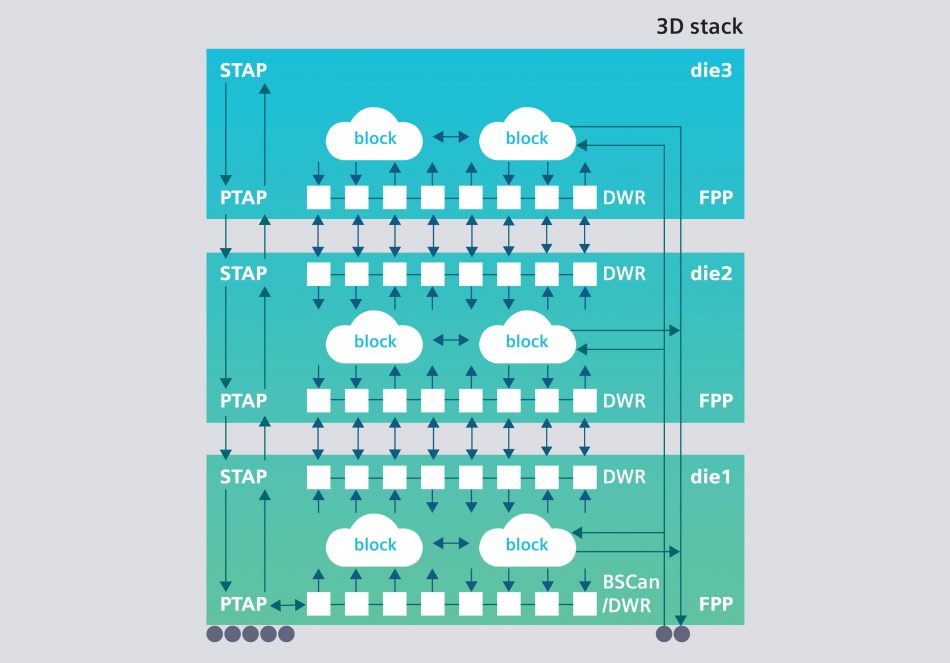

For test, this is already challenging the standards from the established IEEE1149.1 JTAG and IEEE1687 Internal JTAG to the newer IEEE1838 which describes what test engineers need to do to access and implement features for a 3D environment for circuitry and interconnects.

But this is a complex task. 2.5D and 3D designs will frequently comprise ‘chiplets’ from multiple sources, with various inherent test infrastructures. The higher the stack goes the job of applying test also to the interconnects also becomes more complex.

Tessent multi-die brings together adherence to standards with existing efficiency technologies within the suite, most notably the Streaming Scan Network capabilities within TestKompress and Tessent IJTAG features that optimize DFT test resources for each block without concern for impacts to the rest of the design.

Tessent Multi-die adds a 2.5D/3D focused ability to generate die-to-die interconnect patterns and enable package level test using the Boundary Scan Description Language and the integration of flexible parallel port (FPP) technology. FPP is currently described as an option but as the move toward 5.5D accelerates, Siemens says that lead users of the new software have tended to find it essential.

Tessent Multi-die retains the existing look and feel of the rest of the design suite. This addresses engineers preferences but also is one way in which the new product seeks to account for both predominantly new designs and those seeking greater performance though extensive re-use of blocks previously generated for planar 2D designs.

Siemens is presenting the software during this week’s International Test Conference in Anaheim and provides more information on its capabilities here (including a detailed white paper on Tessent Multi-die). Availability is scheduled for the end of the year.