Synopsys targets 5X performance gain with integrated verification suite

Synopsys has further aligned its tools that target the verification gap for increasingly complex SoC design and is to release the bundle as a new product, for monolithic or modular use.

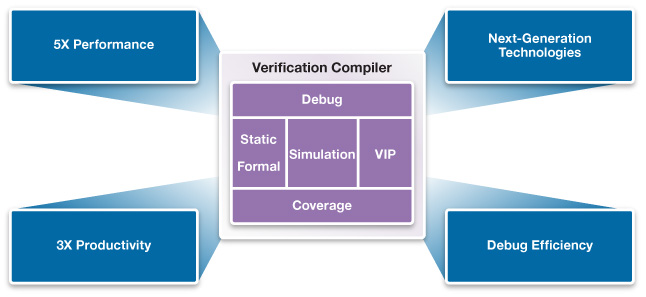

The new Verification Compiler has several main goals.

Key features include:

- Closer integration across the platform means that designs do not need to be recompiled or retargeted for different stages in verification.

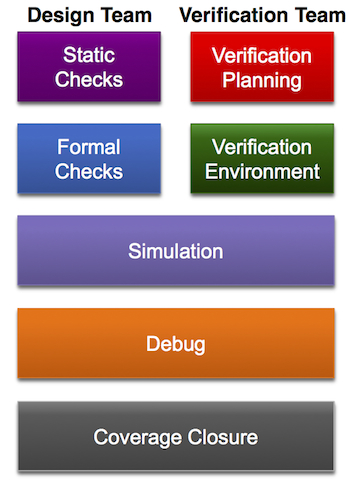

- A single platform methodology enables concurrent verification tasks to be undertaken by the design and verification teams.

- A raft of new ‘next generation’ technologies have been added to the suite, particularly in areas such as low power and formal verification as well as (although previously available but not announced) clock domain crossing and X-propagation.

- The completion of Synopsys’ move to all-SystemVerilog for its verification IP and other enhancements have speeded VIP by 50%.

- Native integration is also available for widely used databases, notably FSDB and Siloti.

- The compiler is also, as you would expect, fully tied into the Verdi debug platform acquired from Springsoft.

Overall, Synopsys says that the package delivers a 5X gain in performance and a 3X gain in productivity.

It is not simply low power designs that have driven Verification Compiler’s creation, although they obviously represent a sweet spot. More generally, the aim is greater efficiency for designs that bring together multiple functions and IP blocks with tight performance, power and area constraints.

The product also reflects the increasing attempts to improve time-to-market by bringing more concurrency to the design flow. The last few months have seen Synopsys active in this area by matching its prototyping products to calls for more hardware/software co-design (see the Tech Design Forum series on Debugging with Virtual Prototypes). Verification Compiler now aims to bring the same kind of efficiencies more explicitly to a hardware flow. This is particularly true in terms of bringing static and formal checks into play at the same time as verification engineers begin planning and creating the environment – a familiar saying here has arguably been modified into “fail to plan early, plan to fail”.

Verification Compiler arrives with endorsements from nVidia, Cavium and Altera (you can read these and more on the product in Synopsys’ multimedia release accompanying the launch). But importantly, it is also available in modular form. So, where customers wish to retain non-Synopsys point tools for certain flow tasks, these can be plugged in but there will still be performance, capacity and productivity gains from the integration of those tools the company does provide. It isn’t Verification Compiler or nothing – that will go some way toward promoting the concept to many users.

Key licensing also reflects demands for greater flexibility and the focus on flow efficiency alongside the technological innovations in Verification Compiler. Every include license will include three keys – one for static and formal verification components, one for simulation and VIP components and one for debug.

“You can use these independently or it can be that the same person uses all of them simultaneously,” says Michael Sanie, senior director at Synopsys for Verification Marketing. “What this means is that whatever stage you are at in your verification, you have the option to do the work concurrently.”

As is the case with most launches (and as the launch endorsements suggest), Synopsys has been working with a number of Tier Ones before the Verification Compiler announcement. One benefit of this is that the company has already started to create a number of cookbooks and best practice guidelines for the product, and will continue to do so.

Verification Compiler is being introduced on the basis of ‘limited customer availability’ right now, with a general release in December.