Synopsys verification IP launch has bite

We’ll be writing more soon about verification IP, but with the launch today (February 27) of Synopsys’ Discovery VIP suite as well as its VIPER architecture, first impressions are that it hits the right grace notes.

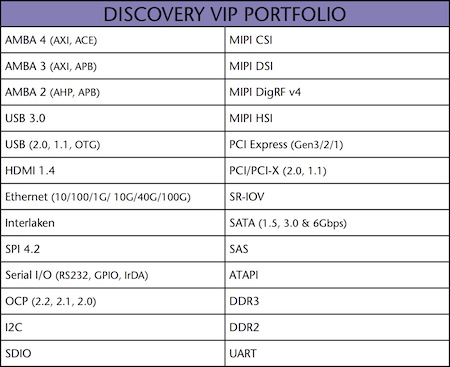

First, it’s in part of the market where engineers are desperate for support. Proliferating I/O for SoCs is repeatedly cited as one of the drivers for ‘endless verification’ and general complexity. It is not that uncommon to have 10 or so different standards sitting on a single piece of silicon. USB, Sata, Ethernet, AMBA, MIPI, PCIe. The only thing I can be sure about there is that I’ve missed something out.

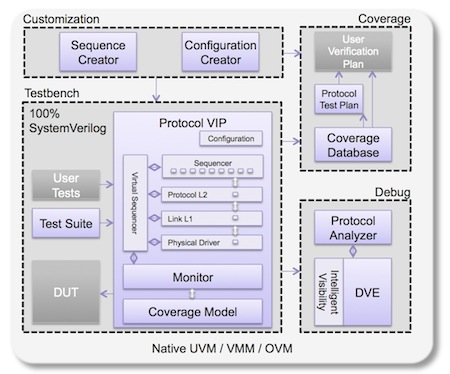

Second, Synopsys has gradually assembled 100% SystemVerilog VIP. This isn’t an overnight launch, rather the result of the years the company has spent backing the language and developing VIP with it in a more discrete sense – it’s both new and a consolidation. However, what matters to the user is speed. With no wrappers to take VIP from ‘e’, C or Vera into a traditional verification environment the hamster will scamper faster (between 2-4X faster helped by a 20% code reduction, Synopsys claims) and should deliver greater accuracy.

Third, and it does need saying, this looks like one of those ‘big is beautiful’ moments. Much of what is happening with Discovery comes back to its creators having been there for quite some time.

- Synopsys has banged the drum hard on SystemVerilog (though perhaps that isn’t too surprising given its foundations in its OpenVera language) and it marks its first official decade this year.

- Beyond that, the company has been building and deepening its IP portfolio generally for a while, so it is close to the standards. With Viper, Synopsys has built functions that it says will use that knowledge bank to speed up the automation and creation of configurations at the beginning, of checking coverage and of running a design against existing debug expertise and experience.

It’s perhaps ironic that the architectural diagram above allocates the smallest amount of real estate to the key areas of customization, coverage and debug, but it does its job in showing how much is being brought together here.

And, with support for all three verification methodologies (as the market coalesces around UVM) that means it can be used with any of the major simulators, including Cadence’s Incisive and Mentor’s Questa. It wouldn’t work otherwise – projects of the complexity targeted here can be distributed across many sites and therefore multiple simulator platforms.

The launch VIP portfolio, meanwhile, while not exhaustive is certainly comprehensive.

With all launches, the real ‘proof’ will now come as customers begin public evaluation. But you can get a more detailed sense of the concept in the multimedia news release and there is also a clear white paper (registration required) by Synopsys’ Neill Mullinger.