April 10, 2012

The article continues the discussion of the verification requirements within the RTCA DO-254 design assurance guidelines. Part Two focuses on assertion-based verification. It proposes a method for using ABV to meet 'elemental analysis' requirements and underpin a systematic approach to robustness testing.

March 20, 2012

Logic glitches in asynchronous clock domain crossing paths can arise even when synthesis tools declare a design’s RTL and gate-level netlists equivalent. This article describes Real Intent’s approach to capturing them.

March 19, 2012

Root-cause analysis of detected errors is a key design step. Debugging can take more than half of the verification effort. Vennsa’s OnPoint automated debug technology has been integrated with Springsoft’s Verdi visualization platform to reduce cost and uncertainty.

March 7, 2012

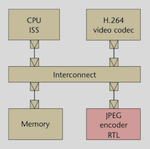

An evolved ESL-to-RTL methodology flow addresses the ‘discipline gaps’ between software and hardware engineering by using three system level-based software-hardware verification steps. The strategy is already available in TSMC’s Reference Flow 12.

February 28, 2012

This two-part article discusses the verification requirements of the RTCA DO-254 design assurance guidelines, including advanced methods for use on class DAL A/B designs. The first part provides a general overview. It also explains the original intent behind the concept of 'elemental analysis', how it is typically satisfied today with code coverage, and the limitations [...]

February 9, 2012

A reference simulator for the latest version of SystemC is now available for public review and comment, writes Accellera's Dennis Brophy. Here's what’s new in the proof-of-concept simulator, and how you can participate to refine the Accellera Systems Initiative’s work for standardization.

January 24, 2012

Functional logic errors remain a significant cause of project delays and re-spins. One of the main reasons is that two important aspects of verification environment quality—the ability to propagate the effect of a bug to an observable point and the ability to observe the faulty effect and thus detect the bug—cannot be analyzed or measured. [...]

January 24, 2012

The inherent complexity of today’s system-on-chips, with their multiple clock and voltage domains, requires test considerations to be moved further up design flows. The article describes strategies for and benefits from apply test before RTL goes through synthesis, augmenting what is already achieved through memory built-in self test and automatic test pattern generation.

January 23, 2012

Virtual prototyping is not a new technique, but the advent of transaction-level modeling and an increased focus on seven key requirements for their effective use means that today's versions are much more broadly applicable and comparatively future proof.

October 19, 2011

The launch of a broad-based IDM/foundry consortium that is to prepare for the shift to 450mm wafers already offers some hints as to the future shape of chip manufacturing and the planning demands it will impose on all design managers in the near future. The game is shifting from pay-for-capacity to outright pay-to-play for those [...]