Analog surges as cause of IC respins (Wilson Functional Verification 2020 – Part Three)

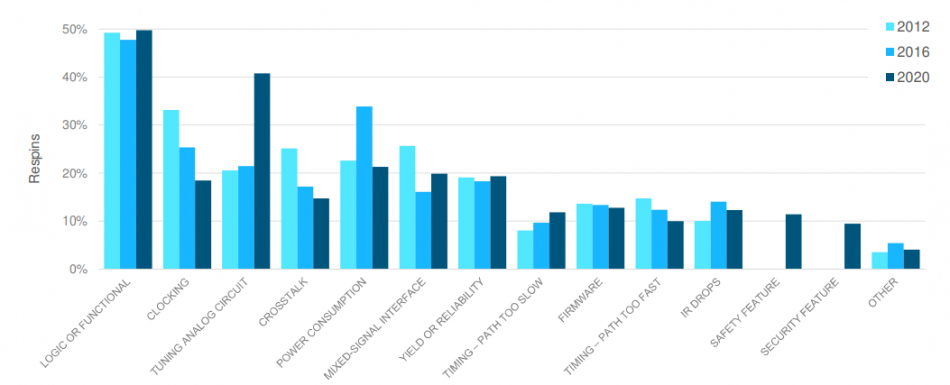

There has been a “huge increase” in analog flaws that have led to respins of IC designs, according to the 2020 Wilson Functional Verification Study. While logic and functional flaws are still the main problem, tuning analog circuitry was cited in 41 per cent of cases. This was almost twice as high as in the 2018 study.

“We are seeing a lot more analog at lower process nodes but the trend was present across the board,” said Harry Foster, Chief Scientist, Verification at Mentor, a Siemens business. “One factor may be that where flows historically have been mostly one-directional – analog-to-digital – there is now a lot more back-and-forth. It’s an issue that needs further investigation.”

The 2020 study, commissioned by Siemens Digital Industries Software, also began to track the impact of safety and security features on designs. Respondents said that 42 per cent of IC designs had a safety-critical element and 54 per cent incorporated security features; in turn, safety was cited as contributing to a respin by 11 per cent of the sample and security by 10 per cent.

A fuller analysis of respin causes is shown in Figure 1 (NB: Several factors can contribute to a respin, so the total exceeds 100).

Figure 1. Type of flaw contributing to ASIC/IC respin (Wilson Research Group/Siemens – click to enlarge)

The challenges that engineers are identifying reflect the latest sources of greater complexity. Alongside more analog, and the needs for greater safety (often standards-driven) and security features, there is also the increasing use of AI. Some 27 per cent of projects in the study incorporated AI processors or accelerators. Then, in a more general sense, 69 per cent had at least one embedded processor and 45 per cent had at least two.

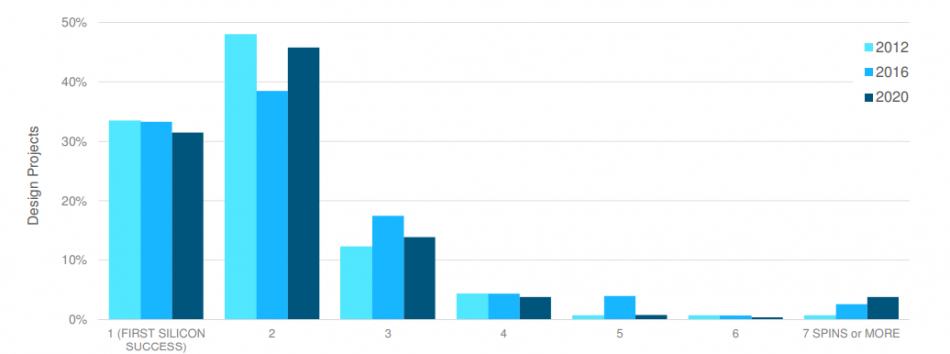

In this environment, the respin count has remained comparatively steady across recent Wilson surveys, although only 32 per cent of 2020’s designs claimed first-silicon success (Figure 2).

Figure 2. ASIC number of required spins before production (Wilson Research Group/Siemens – click to enlarge)

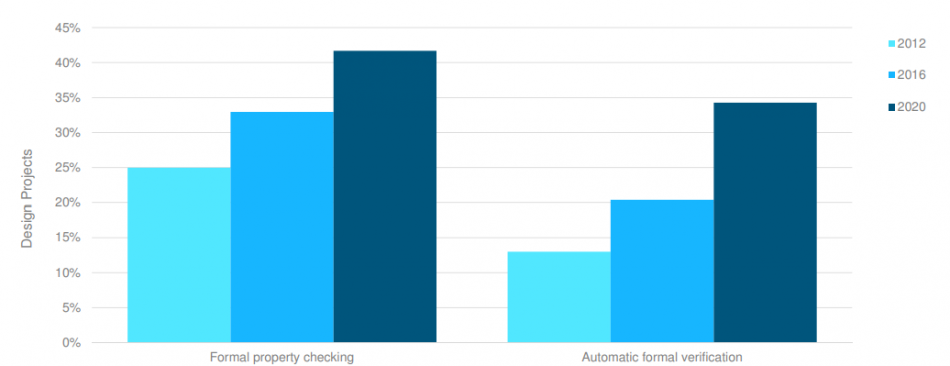

Project managers are turning to a number of technologies to, effectively, hold the line on respins . As in the FPGA market, there is a strong trend toward the use of formal verification in the form of property checking and automated apps (Figure 3). Formal was already more established in ASIC design than in FPGA.

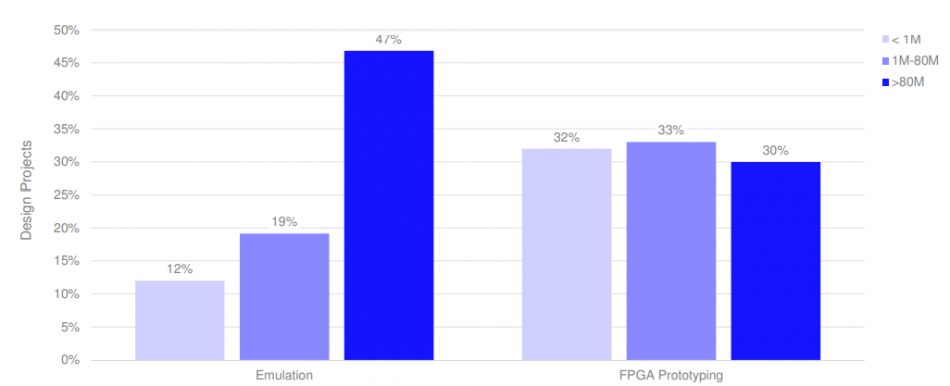

Meanwhile, designs with large gate counts are more frequently using emulation to supplement heavily stressed – and in some cases nearly exhausted – traditional simulation runs (Figure 4).

This is the third in a series of articles on the Wilson Functional Verification Study. The others look at adoption of the open-source RISC-V technology and trends in FPGA design and verification.

You can download Mentor’s analysis of the results for either IC/ASIC or FPGA designs at the following links:

2020 Wilson Research Group Functional Verification Study: FPGA Functional Verification Trend Report