Less than one-in-five FPGA projects avoid bug escapes (Wilson Functional Verification 2020 – Part Two)

Only 17 per cent of FPGA design projects go into production without any ‘non-trivial’ bugs, according to the 2020 Wilson Research Group Functional Verification Study. This can be set against the 30 per cent of ASIC and other IC designs that achieve the broadly comparable metric of first-silicon success.

Alongside the move to system-on-chip implementations, complexity challenges that are currently stressing the FPGA design chain include increasing use of AI IP or some kind of accelerator (19 percent of designs in the study) and the implementation of open-source RISC-V processor technology (23 per cent). Projects must also comply with a wider range of functional safety standards, particularly for markets such as automotive and mil/aero.

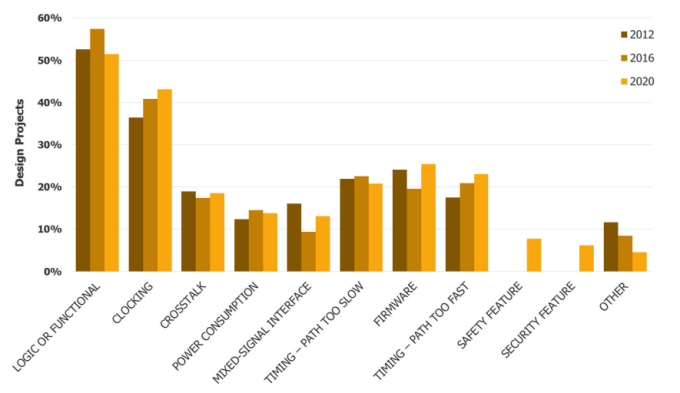

Logic and clocking issues ranked highest among the sources of the bug escapes. Overall, 69 per cent of projects had at least one embedded processor and 45 per cent had two or more. In terms of clocking, 92 per cent of projects had two or more asynchronous domains.

This year saw the study add specific questions about safety and security for the first time, which featured some way down the ranking (respectively at 8 per cent and 6 per cent), although they may still also be captured within other longer-standing data categories.

A fuller range of bug sources is shown in Figure 1. Note that as several flaws may bedevil the same project, percentages can add up to more than 100.

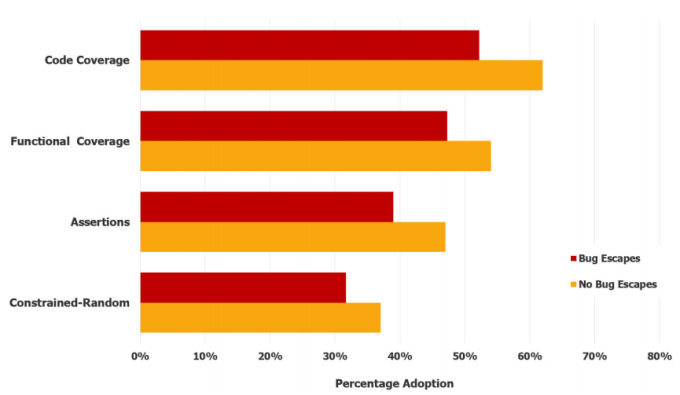

The maturity of respondents’ verification processes did, on inspection, appear to correlate with fewer bug escapes across the adoption of several techniques, notably code coverage and functional coverage (Figure 2).

Figure 2. FPGA simulation technique adoption vs non-trival bug escapes (Wilson Research Group/Siemens)

In the two years since the last Wilson study, there has also been increased adoption of formal techniques. Property checking is sometimes considered hard to master but has still seen 10 per cent compound growth across the last three studies. Automated formal, meanwhile, is now at 21 per cent CAGR for the same period, fueled by both tools and dedicated apps.

Some projects are also seeking to mature their processes by combining design languages. One illustrative example might see VHDL, the traditional FPGA language, used to generate the RTL, but with the testbench then being written in SystemVerilog.

This is the second in a series of articles looking at the results of the Wilson study, as commissioned by Siemens Digital Industries Software. The first article on the adoption of the RISC-V open-source processor can be found here. The second article looks at some of the most significant results in the study for IC/ASIC design.

You can download Mentor’s analysis of the results for either IC/ASIC or FPGA designs at the following links:

2020 Wilson Research Group Functional Verification Study: FPGA Functional Verification Trend Report