RISC-V in nearly a quarter of designs (Wilson Functional Verification 2020 – Part One)

Nearly a quarter of designs incorporate the open-source RISC-V technology, according to the latest biennial Wilson Research Group Functional Verification study.

The double-blind 2020 study, commissioned by Siemens Digital Industries Software, found that 23% of projects in both the ASIC and FPGA spaces incorporated at least one RISC-V processor.

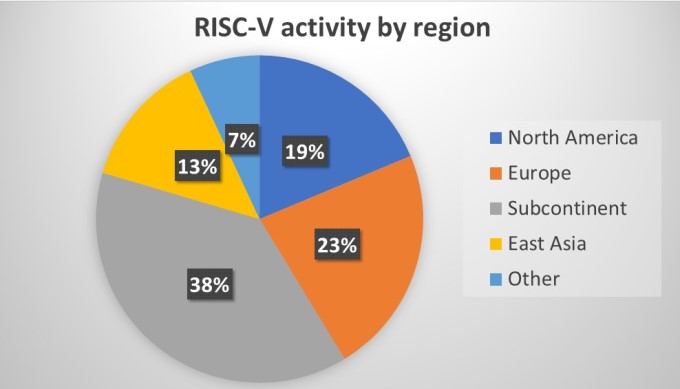

Greatest interest came from India (Figure 1). So much was in line with expectations, but the scale was surprising, according to Harry Foster, Chief Scientist, Verification at Mentor, a Siemens business. This was the first year in which the study has included a specific RISC-V question.

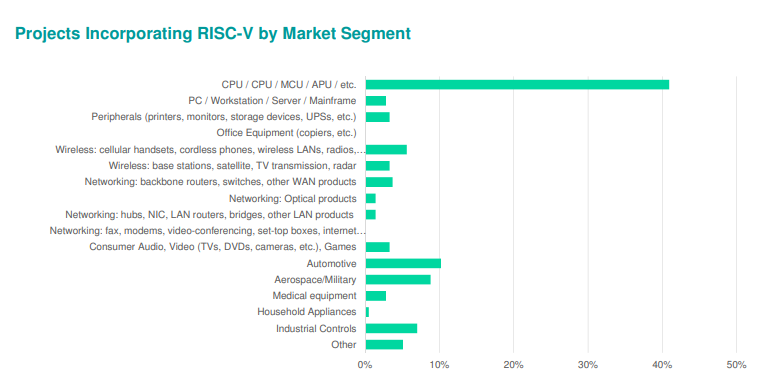

“We’re seeing most of the activity around CPU, accelerators and that block, so a lot of the segments are just starting out but it will be interesting to monitor over the next couple of years, I think we’re going to see a lot of growth,” Foster said.

The study’s design-target results are shown in Figure 2. These point to automotive and mil/aero as the next candidates for rapid growth.

RISC-V adoption began relatively slowly – at least in the eyes of some in the design infrastructure community – but has taken off over the last two years. Building out more tools to support the technology was one of the main themes at this year’s virtual Design Automation Conference.

Notably, the study gathered responses in the June/July period, so many of the RISC-V designs it cites are still to come to market. It is therefore possible that some activity may not have been caught.

Wilson contacted 1,492 designers but there was a shift in responses this year away from North America, with the first wave of the Covid-19 pandemic having its most severe regional impact in early Summer. The still highly fragmented nature of China’s start-up market also makes it difficult to capture design trends there generally, and there has been anecdotal evidence of a rapid growth in local RISC-V activity (possibly reflecting concerns over access to Arm’s rival technology).

The Wilson study also covers general verification trends, including incidence of FPGA bug escapes and the adoption of formal technologies, as well as the increasing integration of AI within designs. The second article in this series on its findings covers the challenges facing FPGA verification. The third looks at the challenges for ASIC/IC verification.

You can download Mentor’s analysis of the results for either IC/ASIC or FPGA designs at the following links:

2020 Wilson Research Group Functional Verification Study: FPGA Functional Verification Trend Report