Mentor builds links for multichip package integration

Mentor, a Siemens business, has formed an alliance with foundries and OSAT providers and launched a flow that brings IC and package design together.

Keith Felton, marketing manager for the Expedition IC-packaging product line, said the company has adopted the term high-density advanced packaging (HDAP) to encompass the system-in-package (SIP), 2.5DIC, 3DIC, and fan-out wafer-level assembly techniques now coming into widespread use.

The aim of the OSAT alliance, Felton said is “to drive a HDAP ecosystem based on these new technologies. The goal is to reduce barriers to entry and to make it easier for fabless semiconductor companies to use these new, emerging technologies”.

Rapid rise for fan-out packages

Felton pointed to fan-out wafer-level packaging being adopted in automotive ADAS implementations as well as mobile consumer devices as market drivers. “These are what we believe are disruptive packaging technologies. They are disruptive to traditional packaging design tools and methodologies. Some of the high pin-count SIP designs are using techniques and methodologies that are borrowed from the IC world. We put them under the umbrella called HDAP.”

Jan Vardaman, president of TechSearch International, said the analyst firm expects a growth of 82 per cent in the use of fan-out wafer-level packaging from 2015 to 2020.

“If you are dealing with a fairly simple flip-chip device you can deal with that using the Expedition traditional tools as you can with the other design tools,” Felton added. “But as you get more pins in the package the cost and complexity goup. You have to start integrating the devices better. Some call it codesign, but you have to optimize the devices together.

“It’s more than the physical connectivity, you have to think about the impact on performance. There is thermal analysis to consider: will you get hotspots if too many functions in a small area are switching simultaneously?”

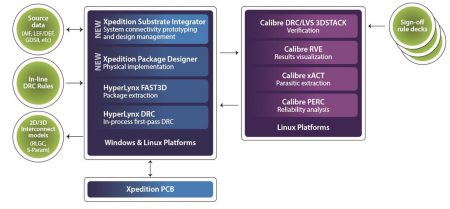

Image Mentor's Xpedition HDAP suite

Mentor took the first steps towards IC-package codesign a few years ago, Felton said, with Package Integrator. “We are seeing more functional integration being required with devices such as more advanced memory. That’s driven us to develop some new technology.”

There is a change in attitude between the IC and packaging and PCB worlds, Felton claimed. “In the IC world, manufacturing drives design. They capture the requirements for high yield in the form of a PDK and you have to design to that PDK.”

The reverse is true of the traditional PCB and package environment, Felton argued. Manufacturers do their best to comply with the demands of designers, up to a limit. But, with finer geometries allowed by silicon substrates, the need to use PDKs has entered the world of the package designer along with more IC-like implementation flow. At the same time, IC foundries are moving increasingly into package provision through 3DIC and fan-out technologies and dealing with the PCB-level issues from which they were isolated before. The merging of ideas and processes is one of the driving forces behind the OSAT Alliance.

Alliance for PDKs

Through the alliance, Mentor aims to work with OSAT providers and foundries to develop PDKs that will support design-rule checks and other aspects of multichip-module design. Members of the Mentor OSAT Alliance will receive software, training, and reference flow best practices from Mentor, in addition to the opportunity for co-marketing mutual offerings. The first member is Amkor Technology.

Ron Huemoeller, corporate vice president, research and development at Amkor, said: “Being an integral part of the Mentor OSAT Alliance program will allow us to fast-track PDK development and delivery, and enable our customers to design more efficiently and predictably.”

The new tools in the Mentor lineup are Substrate Integrator and Package Designer, which includes element of the HyperLynx suite. Felton explained: “Substrate Integrator provides an early prototyping, which is kind of new in the packaging world. You use it describe how you want to connect your devices up and use it construct what-if scenarios. All we really need is a pin-out although ideally you would have an I/O floorplan as that gives you more knowledge about how the device is connected internally and you can see how to swap pins if that is needed.

DRC integration

“Once the prototype has been validated, you push it into design, with a rules-driven, constraints-driven design tool,” Felton added. “Many of the processes require you to follow a stringent set of guidelines. HyperLynx can capture those requirements in its own rules environment and validate that you are complying without having to go externally and run a separate verfication signoff process.”

Direct integration with Calibre provides signoff against the foundry or OSAT provider’s PDK once the design has reached completion. “You can access Calibre’s full set of technologies and use them to compare against a detailed set of signoff rule decks from a foundry or one of the OSAT providers,” Felton said.

The HyperLynx Fast3D package is used to support the creation of detailed models for use by customers for board-level simulation without necessarily having to have the models constructed by a separate group. “We’ve integrated it because we think it’s mandatory for HDAP. We don’t think it’s viable to go to a third-party group to do the extraction.

“And we can feed information to FloTherm,” Felton said, for the construction of detailed thermal models. He said thermal modelling would likely form part of an integrated HDAP toolchain in the future. “So the package designer can create that model.”