verification IP

What is Verification IP?

Verification IP (VIP) blocks are inserted into the testbench for a design to check the operation of protocols and interfaces, both discretely and in combination.

Most standard protocol and interface IP enables verification engineers to check basic features, such as system start-up. VIP enables more detailed exploration. This is becoming increasingly important because of the growth in complexity of system-on-chip (SoC) designs.

VIP can also be used at multiple stages in a design flow and by multiple suppliers to a design project.

Who uses VIP?

There are four main user groups for VIP:

1. Developers of design IP for an emerging or existing specification

These may be in-house teams working on a new design that is aimed at being the first to implement a new specification (increasingly common to match the expanding options demanded on mobile devices) or third parties who want to bring design IP products to market ahead of, or concurrent with, the ratification of a a specification.

2. Early adopters and integrators

This group wants to offer a specification in its early stages and may well be the customers of the third-party companies in the first category. They are particularly concerned to verify a new technology in greater depth as it may not have been used widely and there are consequently issues regarding confidence.

3. Subsystem developers

This group wants each IP block to work independently and but also to check how various blocks interact with one another according to the requirements and capabilities of each specification.

4. SoC developers

With the integration of multiple subsystems and given the size of today’s typical SoCs, this group has two concerns. The first is the interaction between various blocks. The second is that by this time, the design size has become so great that they may need to apply constraint-driven verification techniques and want some form of acceleration.

The impact of IP proliferation

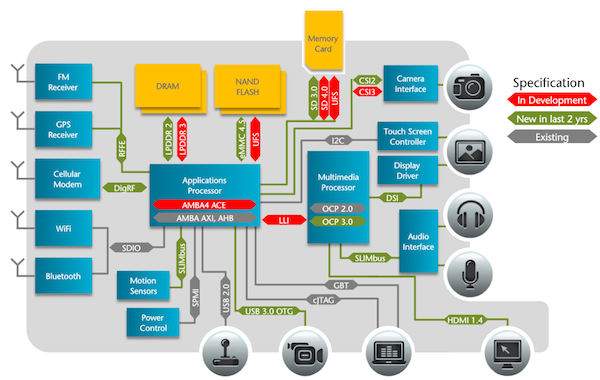

All four user groups are equally important in the design process, but due to IP proliferation, it is the last two that have been responsible for driving much recent innovation in design IP and therefore VIP as well. The following diagram of a typical mobile comms SoC design and the IP that might be integrated within it was originally produced by Cadence Design Systems. It dates from September 2011 and represents the main trends in IP proliferation.

Figure 1

Proliferating specifications in a mobile design (Source: Cadence Design Systems – click image to enlarge)

The diagram shows 27 different specifications for which VIP is required. Of these 12 are fewer than two years’ old and seven are still officially ‘in development’ (although early adopters were already working with them). These emerging specifications represent 70% of the blocks on the design in raw terms, and almost certainly a higher percentage still in terms of the protocol and interface verification effort because of their relative immaturity and greater complexity compared with previous releases.

Another perspective on this issue is offered by the activities of the MIPI Alliance (‘MIPI’ standing for Mobile Industry Processor Interface). Formed by ARM, Intel, Nokia, Samsung, STMicroelectronics and Texas Instruments, it has 15 working groups and, in 2011 alone, released nine specifications aimed at enabling mobile device developers to add more functions to their products. Further specifications were announced at the 2012 Mobile World Congress. MIPI’s prodigious output is in addition to the highly active groups formed around, for example, PCIe, USB, DDR and the AMBA bus specification.

MIPI’s output underlines the extent to which proliferation is being driven by mobility-based devices and the consumer market’s demands for extra functionality with each end-product release. However, the same trend can be seen in desktop and high-performance computing as well as the microcontroller space as it seeks to take advantage of the greater capability offered by 32bit MCU devices.

As noted, it is not simply that the number of IPs is rising fast; the IP blocks are also becoming more complex. A recent analysis by Synopsys noted that the transition from USB2.0 to USB3.0 entailed a potential 20-fold increase in the traffic scenarios that need to be verified alongside a tenfold increase in data traffic.

How is VIP used?

The verification of a typical SoC can take more than half of the total design time. One reason for this is the proliferation of I/O. Memory interfaces are also becoming more complex in order to address issues such as power consumption and latency.

VIP blocks exist in a number of languages (e, C, Vera, SystemVerilog, etc) and will contain options for traditional directed-test scenarios. There is also demand for VIP blocks to work efficiently with verification methodologies such as UVM, OVM and VMM, and to deliver them in ways that cut lengthening verification time. The two largest suppliers of VIP (as well as many of the others) are Cadence and Synopsys, and they are now taking differing routes to meeting this requirement.

With its Discovery launch of SystemVerilog-native VIP in early 2012, Synopsys ensured that its blocks would be compatible with the market’s three main simulators: its own VCS software, Cadence’s Incisive and Mentor Graphics’ Questa. Synopsys argues that choosing to produce its VIP as native SystemVerilog would cut errors in translation, and reduce verification time in other ways. The company outlines its broader strategy here in a February 2012 white paper.

Cadence is staying with and augmenting its current VIP roster in multiple forms, and recently announced additions aimed at the cloud computing market. It has adopted this strategy because, the company says, it preserves the trustworthiness of legacy blocks. Rewrite a block, the thinking goes, and you reset its history. With its acquisition of Denali (then leader in memory IP) in June 2010 , Cadence also got that company’s user interface (UI), which was designed to make its VIP work with any simulator in any language. Cadence has adapted its other VIP blocks to run through that UI. It then allies the UI to acceleration technology at the SoC developer level in pursuit of greater efficiency.

The two strategies illustrate the competition that will play out in the VIP market over the coming months. The main criterion for choosing a VIP vendor is still whether it offers the block you need. Other criteria include the maturity and ease-of-use of the blocks, and how quickly they become available.

Going further, there is the issue of ‘taming’ the development of new specifications and this is also seeing vendors insert their verification experts into the standards drafting process by becoming more active members of groups like MIPI and USB. This not only gives them early insight into new technologies, but also allows them to influence their development so that the resulting specification is easier to verify.

A final issue regards attitudes towards standardized verification methodologies. While the market is coalescing around UVM and it might be said that 80% of the system design industry intends to adopt it, perhaps only a third (or less) today uses it or one of the methodologies feeding into UVM. Nowhere near all design projects do face the massive demands now being placed upon the mobility market, although – and it bears repeating – the influence of trends in mobility is spreading.

Who sells VIP?

The two largest VIP vendors are Cadence and Synopsys. They have gradually assembled libraries that extend beyond fundamental interfaces (e.g., AMBA, USB, Ethernet, PCIe) into highly active and emerging specification families such as MIPI. Both have also led recent consolidation in the sector. Cadence’s purchase of Denali is the biggest deal to date in the VIP business, but Synopsys has also acquired companies such as nSys Design Systems and ExpertIO. Other vendors include:

TVS (Test and Verification Solutions)

USB Type-C: Verification challenges and solutions

Nine effective features of NVMe VIP for SSD storage

What’s cooking at the Flash Diner?

Easing the use of APIs for verification IP stimuli

How to cut verification time with VIP

Ten key tips for effective memory verification