Earlier latch-up prevention with topology-based analysis

A lot of effort goes into the prevention of latch-up. So much is hardly surprising given that occurrence can greatly reduce a device’s functionality or cause permanent damage.

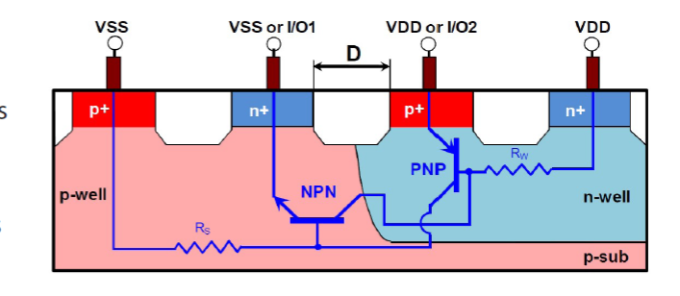

The causes are well known. Parasitic elements within a design can lead to the formation of unintended structures – typically thyristors or silicon-controlled rectifiers (SCRs) – which can then be triggered in the presence of sufficient stimulus and disrupt the original design intent.

Figure 1. SCR cross-section showing parasitic coupling between diffusions connected to VDD and VSS (Oberoi et al)

There are techniques for avoiding a latch-up. Thee mainly involve the use of spacing or guard rings. But the need to add these elements will often only become clear during post-layout electrical rule checks (ERCs), as not only are latch-ups unpredictable but until recently have been largely beyond the reach of the design and verification tools. And the later an issue is discovered – even, hopefully, before a product release – the more expensive it is to fix.

A recently published white paper describes how Mentor, a Siemens business, has extended its Calibre PERC reliability platform to introduce a topology-led and automated approach to latch-up verification. This has the advantage of being available for use earlier in a flow, specifically during schematic design.

By concentrating on topologies, the tool can, explains author Flint Yoder, identify ‘sensitive’ scenarios such as MOS devices with direct and low resistance connections to I/O ports (these can allow a carrier injection to reach a parasitic thyristor more easily) and structures that use grounded or biased N-wells (these are more sensitive than alternative structures). Taking an overview of operating voltages also helps to identify potentially problematic circuitry.

The goal behind the automated analysis, described within the paper, is that designers can either apply latch-up mitigation such as guard rings or avoid the use of problematic design elements entirely.

“By running Calibre PERC verification on the schematic netlist during early design phases, designers can quickly identify latch-up sensitive scenarios through topological analysis. Latch-up scenarios can then be resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting,” Yoder writes. “Additionally, early identification of latch-up sensitive elements placed within or created by the design circuitry allows designers to mitigate any potential failure conditions that cannot be removed by making informed decisions during later chip development.”

‘Robust latch-up protection with schematic netlist circuit verification’ is available for download at this link.