Case study: Achieving earlier signoff convergence and a ‘shift left’ for P&R at Qualcomm

Mentor launched the Calibre RealTime Digital tool in June. It graphically flags DRC errors during place and route (P&R) of digital blocks within the layout software., The engineer therefore does not need to review the documentation from a full DRC fun.

This article describes Qualcomm’s experiences in India with Calibre RealTime Digital as a pre-release user. It describes the background to its decision to extend the tool’s use as part of its core company-wide design flow.

Qualcomm challenges

Qualcomm was suffering DRC-based delays in achieving P&R sign-off and convergence that it attributed to a number of sources. Among the most significant were:

- Late stage IP integration leading to nwell, diffusion and fin boundary violations;

- Incorrect and unintended metal fixes; and

- Standard cell interface errors, sometimes hidden by a proliferation of surrounding metal DRC issues.

Correcting these errors was a largely manual and iterative process. P&R-based DRC would be run. The report would be analyzed. The routing would be amended. P&R-based DRC would be run again. The new results would be reviewed, and then the routing might well need to be amended again. Cycling through these steps added days and sometimes weeks to the overall design process.

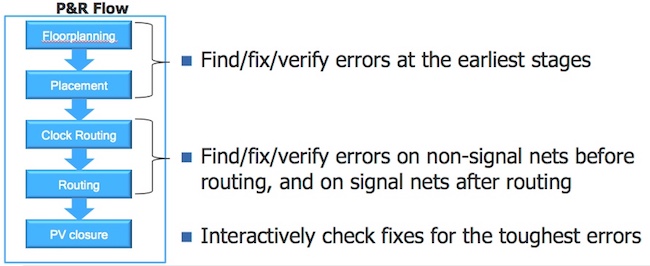

A second objective was Qualcomm’s wish to achieve a ‘shift left’ in its DRC process. Here, the company wanted to save time by bringing forward the physical verification feedback process and thereby achieving greater design convergence earlier (Figure 1).

Before introducing Calibre RealTime Digital, its designers had:

(i) Exported the P&R database.

(ii) Generated GDS files

(iii) Run standard Calibre DRC

The quality of the resulting P&R database had led to LEF vs GDS format errors that could again take significant time to resolve. In a wider sense, Qualcomm was concerned that DRC runs were taking up too much time at critical points in the design flow.

Adopting Calibre RealTime Digital

Calibre RealTime Digital analyzes a P&R layout based on foundry-approved DRC rule sets and displays the results graphically. It flags DRC violations in the layout screen rather than through a report that needs to be separately read and understood.

It is compatible with and provides such results within the GUIs of all major P&R software suites, including Innovus from Cadence Design Systems and IC Compiler II from Synopsys. As such, it is not disruptive in terms of design-flow adoption. If anything, it aims to present violations data in the context that is easiest for P&R engineers to analyze.

Qualcomm specifically used the tool’s IP Merge function to read in IP blocks, including late additions and to replicate the metal geometries within those blocks.

The company said that this allowed it to apply fixes in one or two runs and a few hours in comparison with a flow that had been taking several days.

“Fixing becomes very intuitive and we can instantly validate the fixes. For complex DRC rules it really helps to get feedback within few seconds compared to hours for a standalone run,” said Satish Dinavahi, Director, Engineering at Qualcomm India.

Qualcomm’s results

The main conclusion Qualcomm reached benchmarking Calibre RealTime Digital against its previous flow was that the tools saved between three and five physical verification iterations during each critical milestone for P&R. It provided greater confidence that the P&R results would have sufficient convergence for their translation into a fab-ready format. It also lead to a ‘cleaner’ design entering the final Calibre DRC stage before being sent to manufacturing.

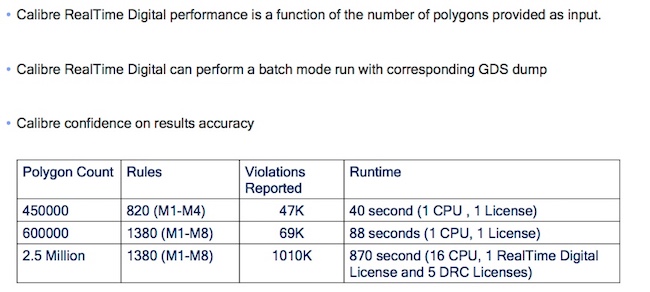

The company also found that the tool’s performance was a function of the number of polygons provided as input, data shown in Figure 2.

Future application

Qualcomm’s first deployed Calibre RealTime Digital within the digital design group inBangalore, India. Based on the results, it now plans to extend it across the P&R flow at more locations.