Mentor targets DRC efficiencies for place-and-route with Calibre RealTime Digital

Mentor, a Siemens business, is extending its Calibre suite with a new tool aimed at vastly reducing the time spent correcting DRC errors during physical verification of digital designs.

Calibre RealTime Digital, which is available immediately, allows designers to make small and custom corrections after a place-and-route DRC run without forcing them to refer manually to all the errors it has found.

Reviewing documentation, re-running DRC and making fixes has historically been a lengthy process. Not only do designers need to understand what the DRC report is actually saying, but they can also find that each iterative fix simply causes more errors itself.

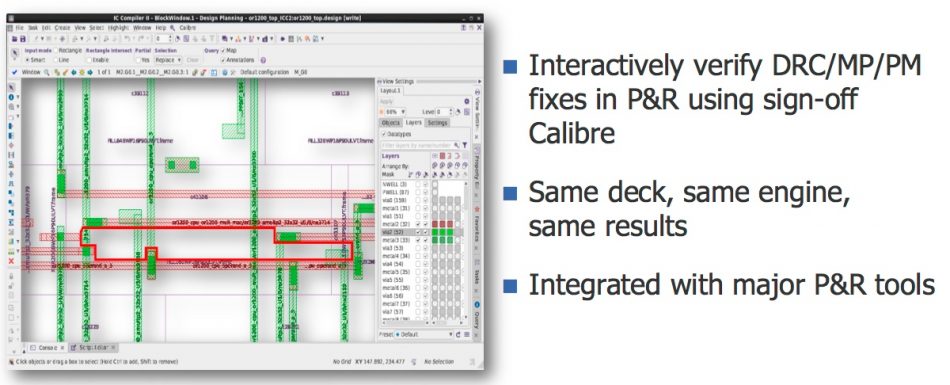

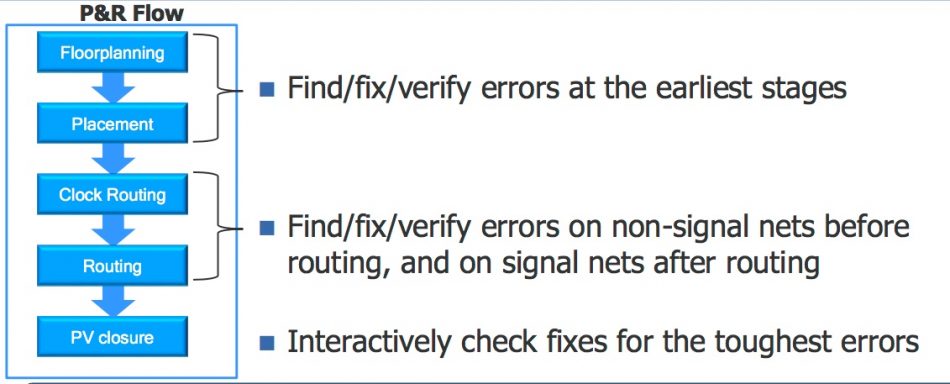

Calibre RealTime Digital aims to allow designers to review and fix graphically-flagged errors in situ and receive a report. It does this in part by constraining the necessary DRC check afterwards to those areas that have been altered. The overarching goal is to closely embed DRC within the user’s P&R environment.

Early user Inphi found that using the interactive Calibre RealTime Digital tool allowed it to cut the time it needed to sign off a DRC block by 40%. Another unnamed user claimed a reduction of 80%.

Srinivas Velivala, Product Manager with Mentor’s Design to Silicon Division, said users that have had early access to the tool have found its interactive features useful at flow stages before physical verification (Figure 2).

However, the driver behind the introduction of Calibre RealTime Digital has been the further growth in DRC errors emerging at more advanced nodes. For 7nm, Velivala said a flag increase in the 2X range has been reported.

The tool has been fully integrated with major P&R software such as Innovus from Cadence Design Systems and IC Compiler II from Synopsys. As it also uses the existing Calibre DRC decks, it is also foundry-qualified by default.

Learn more about Calibre RealTime Digital

Calibre RealTime Digital is a flagship release for the forthcoming Design Automation Conference in San Francisco where Inphi and also Qualcomm will discuss their use of the tool at the Mentor booth (#2621).

The Inphi presentation is scheduled for Tuesday June 26 at 4pm and Wednesday June 27 at 10am. The Qualcomm presentation is scheduled for Monday June 25 at 10am, Tuesday June 26 at 3pm and Wednesday June 27 at 2pm.

Users who cannot attend this year’s DAC can find out more about Calibre RealTime Digital on its dedicated web page, where a white paper from Inphi and datasheet are also available.