Xpedition updated for schematic verification and DFT

The latest Xpedition Verification Platform from Mentor seeks further to address a PCB market where more than half of projects miss their release dates or original budgets, with that number going higher for bleeding-edge designs in areas such as high-speed.

In common with earlier releases, the new additions share a ‘shift left’ objective to integrate verification tasks within earlier stages of design. They address schematic verification and design-for-test.

The company has also deepened the integration of existing features for vibration, DC drop, electrical rule checks and DFM.

The respin ramp

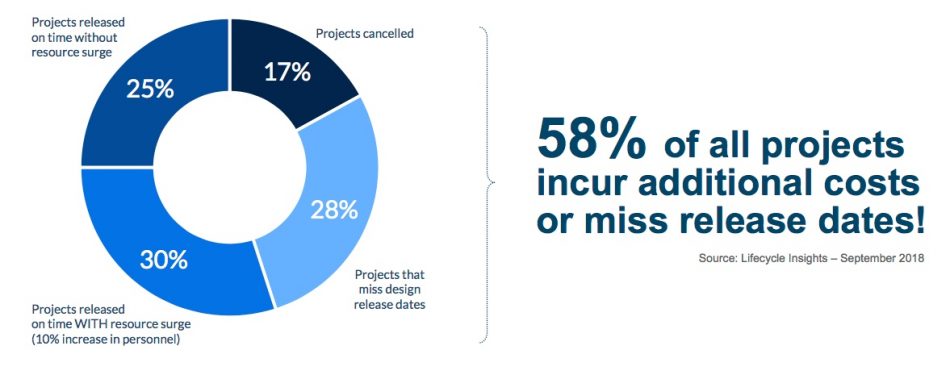

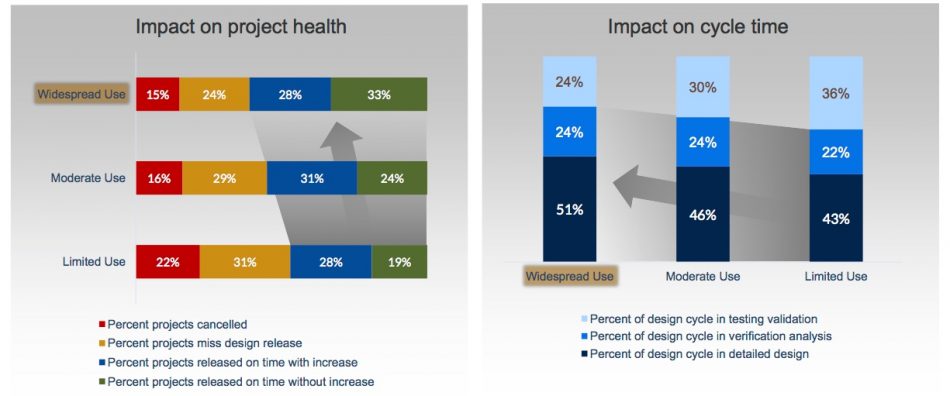

Mentor is supporting its Xpedition launch by releasing independent research conducted earlier this year by Lifecycle Insights.

It concludes that only 25% of projects are delivered on time and on budget, while 17% are cancelled. Average spins per project are running at 2.9 at an average per-spin cost of $44,000 in money and 8.5 days in time.

At the same time, Lifecycle found that those companies which use more extensive and advanced methodologies are already seeing a 14% improvement in project delivery.

Mentor proposes a strategy for addressing these challenges that allows ‘design authors’ – schematic authors, layout designers, etc – to capture first-order fails within their native tool environments. They can then correct basic errors before a design is passed on for more detailed analysis by verification experts.

This approach is illustrated by how it is positioning the two new features in Xpedition.

Automated schematic verification

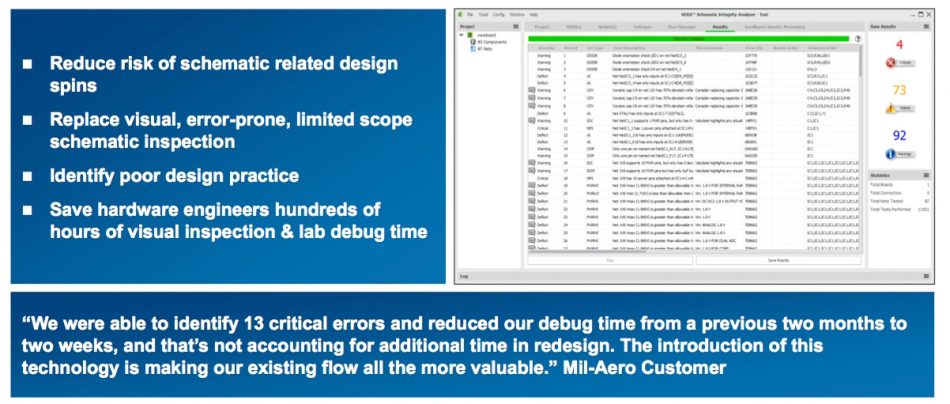

The new automated schematic verification feature in Xpedition has more than 150 ‘voltage-aware’ rules which are used to review an in-progress design to identify common errors and test all nets within either a single or multiple PCB design.

These kinds of check have historically been carried out manually, largely by peer review and can take weeks to complete. Even then, there is plenty of scope for human error given the many thousands of nets involved.

Mentor says that Xpedition can now automate the same analysis provide a simple report, one that will continue to grow in granularity as more rules are added all the time. Potential design issues are then fed back to the schematic engineer for early-stage correction/review as ‘Criticals’, ‘Defects’ or ‘Warnings’.

Mentor cites the experiences of a pre-release user in the mil/aero market who said the feature helped reduce its typical debug time from two months to two weeks, even before redesign work was included.

The schematic verification feature is based on technology Mentor acquired from specialist start-up Valydate last Summer.

Integrated testability analysis

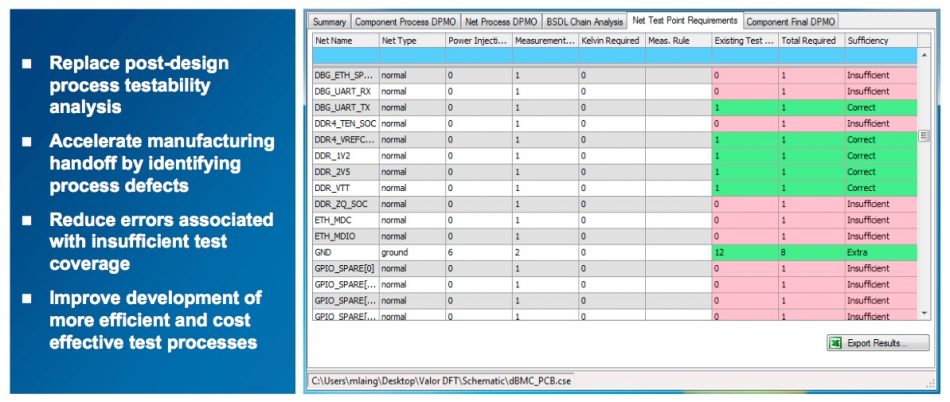

The integrated testability analysis feature seeks to replace a process that has been largely based on rules of thumb, guesswork and, again, manual effort.

It identifies appropriate test points within a schematic based on factors such as their position relative to trace widths and the reliability ratings for components within the design. These requirements can then be automatically passed within Xpedition to PCB layout.

The automated process is again manufacturing-aware and designed so that problems with coverage and test point insufficiency are addressed as early in a project as possible, and by the engineer who first needs to consider them.

Xpedition vs ‘Not done here’

Mentor is taking as much as metrics- as feature-led approach to rolling out its latest Xpedition extensions because there is a lot of entrenched conservatism about tool purchases in the PCB market. There is also the need to consider the boundary between core design work and reviews undertaken afterwards by technology analysts.

As PCB complexity grows – compounded by both higher speeds and a greater number of boards within system – the market is also facing much higher demands in terms of reliability (the classic example being those now being imposed for automotive designs).

In that context, the company is arguing that ‘good-enough’ tooling may now longer be enough, further illustrated by the fact that respin costs are now moving into six figures. They might still be some way off the million-dollar-plus respins seen in silicon, but they are undoubtedly growing at an increasing rate relative to typical PCB budgets for both time and money.

To that end, Xpedition’s new features primarily target what are seen as ‘first order’ concerns, rather than those that arise as projects are pushed closer to the bleeding edge. Let the core designers pass cleaner work to the experts so that they can concentrate on their specialist areas with greater confidence in the rest of the work.

Mentor has produced a set of strong supporting material to make its case, alongside the Lifecycle research.

A YouTube video explains more about the new features and their context. There is also a white paper and a webinar on them. And you can learn about the updates at the main Xpedition website.