Layout schema generation speeds early-stage yield learning

Legacy designs only take you so far when you are doing pre-ramp yield optimization for a new process node. As well as the challenges posed by new manufacturing technologies, there is also the likelihood that further random, systematic and parametric defects will emerge that require extra design rules and strategies.

An emerging technique, layout schema generation (LSG), aims to make early-stage yield-learning far more efficient.

Layout schema generation

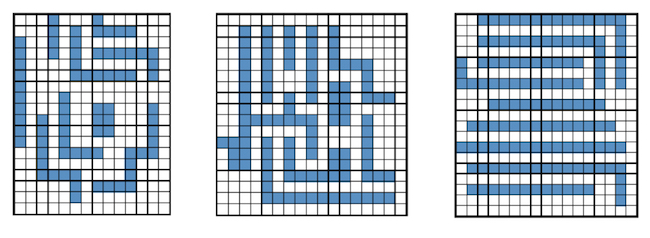

LSG is based on the generation and random placement of unit patterns on a test macro that can nevertheless be scaled into meaningful larger patterns. The LSG process is based around specifications that will make these patterns look like typical designs according to the initial set of design rules for a new process. The user can also add circuitry to make the chips measurably electrically.

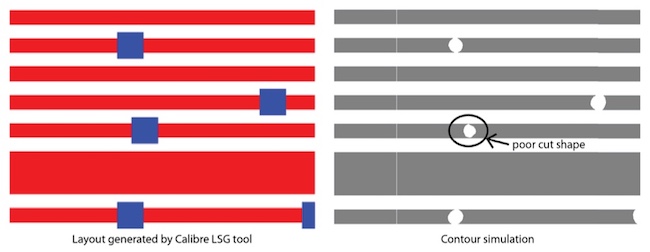

Mentor, a Siemens business, has introduced LSG on in its market-leading Calibre physical verification suite. A new technical paper from the company both describes LSG in more detail and details its experimental application for self-aligned multi-patterning (SAMP) test vehicles.

LSG for SAMP test macros

SAMP, within an 193nm immersion lithography process, is one of the leading candidates for use at the incoming 7nm and 5nm nodes. It also presents the challenge of being a technology where there are a considerable number of defect-generating ‘known unknowns’.

Two SAMP-based specific experiments are described in the Mentor paper. One addressed the detection of random conducting particles. The other considered the detection of problems with systematic cut-mask resolution. The randomly generated LSG vehicles resulted in a faster modeling of defect density and the identification of poorly resolving shapes.

“Our experiments with [LSG] technology show it can provide high coverage for new design styles for an arbitrarily wide design area,” write authors Wael Elmanhawy and Joe Kwan. “The ability to discover lithographic hotspots early in the technology development process is significantly improved, at the expense of additional testing area.

“Design and process co-optimization of the discovered hotspots speeds up the yield optimization.”

Improving Yield for New Design Styles During Technology Development is available for download in full here.