September 18, 2012

Carbon Design Systems' CTO Bill Neifert argues that his company's deal with Samsung sends a clear signal, whether or not you're one of his customers.

March 28, 2012

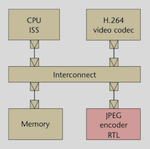

How SystemC enables system modelling at higher levels of abstraction, and the creation of virtual platforms.

March 7, 2012

An evolved ESL-to-RTL methodology flow addresses the ‘discipline gaps’ between software and hardware engineering by using three system level-based software-hardware verification steps. The strategy is already available in TSMC’s Reference Flow 12.

February 9, 2012

A reference simulator for the latest version of SystemC is now available for public review and comment, writes Accellera's Dennis Brophy. Here's what’s new in the proof-of-concept simulator, and how you can participate to refine the Accellera Systems Initiative’s work for standardization.

January 29, 2012

Transaction-level modeling (TLM) describes a system by using function calls that define a set of transactions over a set of channels.

January 23, 2012

Virtual prototyping is not a new technique, but the advent of transaction-level modeling and an increased focus on seven key requirements for their effective use means that today's versions are much more broadly applicable and comparatively future proof.

August 23, 2011

We report from National Instruments’ annual user conference, NIWeek 2011, held in a sizzling Austin last month.

August 23, 2011

Mentor’s Dennis Brophy, Cadence’s Stan Krolikoski and Synopsys’ Yatin Trivedi describe how you can prepare to adopt Accellera’s Universal Verification Methodology.

June 1, 2011

Leading chip design analyst Gary Smith charts the course through the main questions dominating DAC 2011.

February 25, 2011

The article is abstracted from a presentation given at NASCUG by Umesh Sisodia and originally developed by Ashwani Singh of CircuitSutra Technologies on how to create adaptors between various modeling abstraction levels in SystemC.