The new semiconductor ecosystem: wants and needs

Leading chip design analyst Gary Smith charts the course through the main questions dominating DAC 2011.

We are now seeing the new semiconductor ecosystem rapidly taking shape. My EDA clients have been asking me what is going to be hot at DAC. Unfortunately the questions I am being asked by my semiconductor clients this year cover a fairly lengthy shopping list, stretching across everything from system design to emerging fab strategies. I think the best way to cover this for DAC is for me to comment on some of the more commonly asked of those questions. These fall into six areas:

- Behavioral level ESL

- The three ESL virtual prototypes

- Automating the analog design flow

- RISC vs. CISC

- The third-party IP market

- The emerging foundry market

Behavioral level ESL

This is not a new request but one that has taken on a sense of urgency. When will we have behavioral level SystemC (or possibly C/C++) modeling standards? As application-driven design becomes the norm we need to be able to simulate our system designs. This cannot be done without behavioral level modeling standards. We have M and UML, but the real leap in productivity will come with a SystemC or C/C++ standard. Oh, and don’t confuse application modeling with application software. They are two different subjects. Application software is not developed until you drop down to the architectural level of ESL.

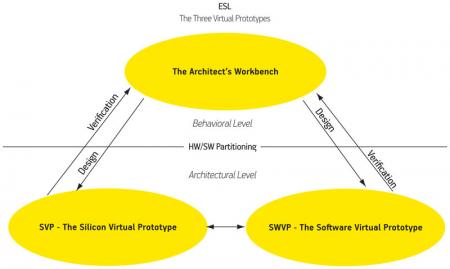

The three ESL virtual prototypes

A lot of the confusion in ESL design centers around the use of virtual prototyping. One of the most common questions this year has been, “Please explain to me the ESL virtual prototyping environment?” The EDA vendor’s presentations are confusing. Most of the confusion comes from the fact that there are three different virtual prototypes and most vendors are not telling you which one they are talking about. I have come up with a fairly simple diagram (Figure 1) that points out the differences.

Figure 1

Virtual prototyping environments

Source: Gary Smith EDA

Next time you see a presentation on ESL virtual prototyping, ask the vendor which one he is using before he starts. If he doesn’t know, don’t bother sitting through the talk.

Automating the analog design flow

There has been a mismatch between what the mixed signal designers are asking for and what the EDA vendors are introducing. The new analog tools are needed, but with today’s design challenges we need to take analog to the next level. The question here is, “When are we going to have an RT level flow for Analog?” Actually there are already requests for ES level design tools, but until we have an RT level design flow they will not do us much good. In 2001, I did a presentation on an RTL analog flow based on my experiences at Telmos, my first start-up. I have passed it around and the response has been positive. Basically what we need is the following:

- A standard gate-level analog library. We had one at Telmos. Keep in mind the reason Synopsys captured the RTL synthesis market is that it targeted the IMI/LSI Logic gate-level library. At the time, most ASIC vendors were using a version of IMI’s library, and LSI Logic had done an exceptional job of enhancing it. The standard was in place and all Synopsys had to do was develop a synthesizer using the standard.

- The development of an RT level analog synthesizer. What passes for analog synthesis today are analog compilers working at the transistor level. That is way too low a level for today’s large analog designs.

- Real movement on analog BIST. We had some attempts back at the turn of the century but they seem to have died off. There are a few start-ups popping up today so there is hope. Without solving the analog test problem all our work on analog design automation will be worthless.

We have adequate RT Level mixed signal simulators, so we are OK there. Once the components above are in place, we can start on the ESL analog tools. Actually, one start-up, EDANova is working on one, but with start-up funding the way it is they could use some help.

RISC vs. CISC, CPU vs. GPU

What the #&!! is going on in the microprocessor market. Actually, the question is, “Which processor architecture should I concentrate on?” What is actually going on is the development of a microprocessor cluster architecture in which the general purpose CPU will play an increasingly smaller part. These clusters are reconfigurable and will use the domain-optimized processors (DOPs) needed for the specific applications required by the platform. Today’s competitive semiconductor environment is all about application platforms that are used as the base for gigantic SoC designs.

The third-party IP Market

There actually is not as much confusion in the semiconductor market on third-party IP as there is with the press and some EDA vendors. With the move to very large IP blocks (i.e., a million gates and up), there has been a move back to internally developed IP. That is because of the requirement for modifiable IP at that level. Modifiable IP is a macro that you can take out and/or replace sections of without severely affecting the verification of the IP. This is a major challenge for the third-party vendors, hence the move to in-house IP.

If you look at the rest of the market you see the star IP vendors starting to develop platforms of their own, as sub-systems for the semiconductor companies’ applications platforms. The rest of the IP market, with the possible exception of analog IP, goes through the familiar cycle of:

1. Royalty based IP

a. Non-royalty based IP

i. IP as part of a library

1. IP sold along with an EDA tool

a. IP bundled in with an EDA tool

i. Free IP library given to a customer to support an EDA tool

If you look at IP today you basically see ARM, with star IP, and Synopsys, with library IP, owning more than half of the market. Add the analog and memory IP vendors and there is not much left for the rest. Unless other third-party IP vendors can break into the modifiable IP market, it looks pretty stagnant today.

The emerging foundry market

This has been driven by the recent pronouncement that only three companies can meet the $6B price tag for a state-of-the-art fab. The usual question here is, “What should my fab strategy be in the next ten years?” I think the main problem is that the definition of ‘fab-lite’ you hear in most presentations is not a sustainable strategy. Once you drop off the leading edge, you might as well not have a fab at all, with the exception of some analog, RF or power semiconductor vendors. The power an IDM possesses comes from control over the manufacturing process. What you want to outsource is your high-volume production, your home runs. Fortunately, that is exactly the kind of business the foundries love. They want it so much that they are quite willing to modify their process for you.

So looking at an IDM’s business model today, you see the main cost is in process research. Process development is not that expensive. This means you join a consortium, such as the Common Platform consortium that IBM leads. I am expecting that Intel will get into the consortium business sooner or later, so that leaves TSMC. They may not take the plunge. But if they do not, I expect another consortium will emerge to stabilize the market.

What does that mean for the IDMs? Most important, they do not need a high volume fab. They can use a standard fab with a capacity of about ten thousand wafers per month. That will cover most of their customers’ demands. Even the automotive market fits into that volume fab model. It should cost $1B or less—high but affordable. They can stay on the leading edge of semiconductor technology and be able to modify their processes to fit their own needs. For their home runs, they can go to the high volume fab (or fabs) associated with their consortium. In the end, I believe we will see around 50 IDMs taking this approach. Maybe we should change the strategy to ‘fab-standard’ rather than ‘fab-lite’.

Conclusion

That takes care of the most frequently asked questions. Even that partial list gives the semiconductor ecosystem plenty to work on. As I have said many times before, this new world of design will give all vendors plenty of opportunity to grow. Think of this as the first year of the future and you will be able to take advantage of this new marketplace.