August 23, 2012

The verification challenge is best addressed by a combination of highly targeted tools, according to Pranav Ashar, CTO of Real Intent.

July 26, 2012

Assertions are already used in pre-silicon verification and can help halve debug time. So why not synthesize assertions into real logic gates in the final silicon, to catch those unexpected bugs that make validation so much harder? Here’s how.

May 21, 2012

An overview of the Open Source VHDL Verification Methodology and two of the libraries it uses.

April 25, 2012

Can emulation save energy and space, as well as time, during the verification process? Some argue so.

April 25, 2012

Richard Pugh reflects on efforts to cut through the tangle of cables and make emulation easier.

April 24, 2012

This extract from the Synopsys and Xilinx-authored "FPGA-Based Prototyping Methodology Manual" outlines a number of valuable strategies supported by brief project case studies.

April 10, 2012

The article continues the discussion of the verification requirements within the RTCA DO-254 design assurance guidelines. Part Two focuses on assertion-based verification. It proposes a method for using ABV to meet 'elemental analysis' requirements and underpin a systematic approach to robustness testing.

March 20, 2012

Logic glitches in asynchronous clock domain crossing paths can arise even when synthesis tools declare a design’s RTL and gate-level netlists equivalent. This article describes Real Intent’s approach to capturing them.

March 19, 2012

Root-cause analysis of detected errors is a key design step. Debugging can take more than half of the verification effort. Vennsa’s OnPoint automated debug technology has been integrated with Springsoft’s Verdi visualization platform to reduce cost and uncertainty.

March 7, 2012

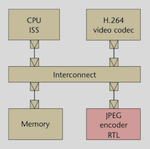

An evolved ESL-to-RTL methodology flow addresses the ‘discipline gaps’ between software and hardware engineering by using three system level-based software-hardware verification steps. The strategy is already available in TSMC’s Reference Flow 12.