Use equivalence checking to retarget obsolete FPGA designs

Many obsolete FPGAs can carry designs that remain valid and whose performance can be enhanced by moving them across to current devices with new features and lower power consumption. Equivalence checking forms an important and necessary part of the retargeting process.

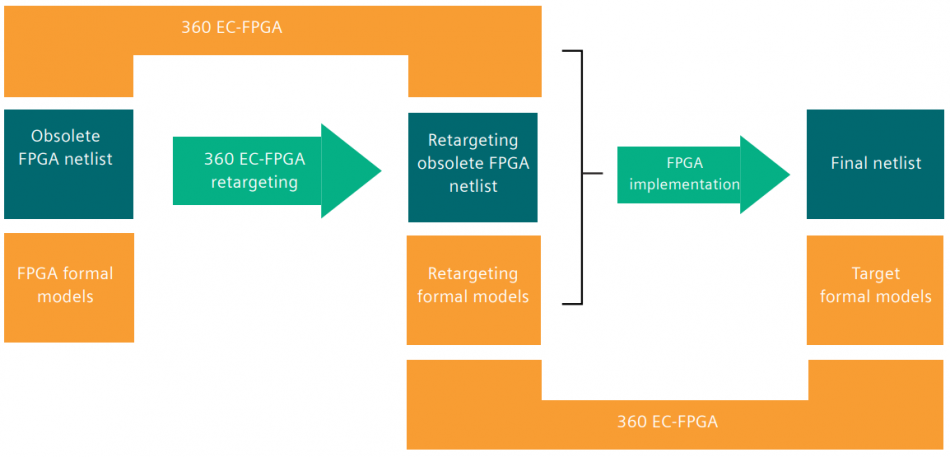

A new technical article, ‘360 EC-FPGA retargeting flow‘, considers the various retargeting scenarios available in depth and in the context of the Siemens EDA’s automatic sequential equivalence checking tool. It describes an overarching retargeting flow (Figure 1) and three further verification scenarios:

- Equivalence with RTL: where RTL is verified against an obsolete netlist if it has not been modified.

- RTL retargeting: where RTL for the obsolete device’s netlist can be reused for resynthesis and retargeting.

- RTL-RTL retargeting: where the obsolete device’s RTL contains IP that is no longer valid and is being replaced by up-to-date versions.

Figure 1. 360 EC-FPGA retargeting methodology including equivalence checking (Siemens EDA – click to enlarge)

Both the processes and key code elements for all these equivalence checking approaches are described in detail.

“The retargeting flow prevents costly, time-consuming, and resource draining re-design. Because this flow is independent of the capabilities within the new target device, the trust and security, safety, and power saving features

of the new FPGA devices are all supported by this flow,” the paper argues.

“The RTL retargeting flow can be used to ensure that the obsolete device netlist functionality is retained in the new device netlist resynthesized using the original RTL.”

The paper methodology and guidelines are available for download here.