Learn how Renesas uses SLEC to enhance its verification flows

There has been a lot of debate in the last three years over the use of formal equivalence checking to add greater certainty to high-level, early-stage verification. It resolves many of the challenges that exist toward taking SystemC descriptions smoothly through to RTL sign-off.

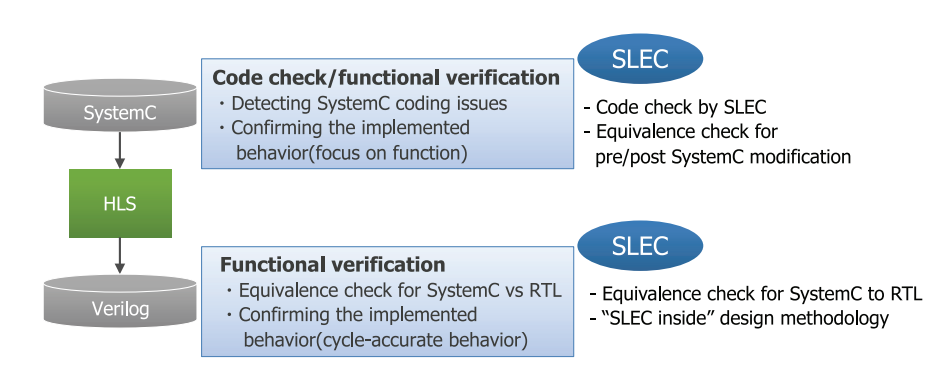

A new technical paper describes how one leading semiconductor company, Renesas Electronics, added the sequential logic equivalence checking (SLEC) tool from Mentor, a Siemens business, to its flow, ultimately using it during both SystemC and RTL verification.

The paper describes how the tool is now being used during both stages and was introduced into the company’s design processes. It details the time savings and better coverage achieved, as well as the company’s thoughts on next steps.

Figure 1. An overview of how Renesas integrates SLEC within its SystemC and RTL verification processes (Mentor/Renesas)

In Renesas’ case, the company found that verification iterations were reduced and verification time cut by several orders of magnitude.

‘Renesas solves verification in high-level design using formal equivalence checking‘ is available for immediate download.