Module verification demands integrated DRC and LVS

The trend toward combining multiple modules and chiplets within system-in-package (SIP) design poses major challenges for system-level verification, with a combined and integrated design rule check (DRC)/layout vs schematic (LVS) process seen as increasingly necessary.

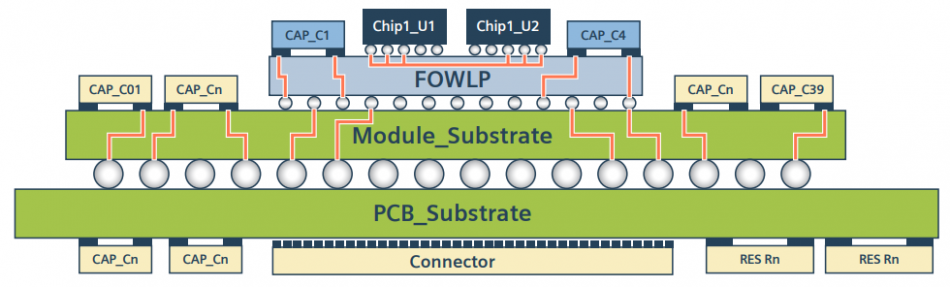

Bringing together DRC and LVS combines the two techniques to consider physical and electrical concerns in the same context. It can prevent the late-stage emergence of problems related to unintentional shorts or opens, misalignment, die shrinkage and more. But what does such an integrated flow look like. These designs are extremely complex and can have many separate contributors, internal and third-party (Figure 1).

Figure 1. Module designs include multiple dies, dozens to hundreds of passives, and multiple substrates. This data, often owned by different teams, must be consolidated (Siemens EDA)

A new how-to article describes a DRC/LVS strategy based on Xpedition Substrate Integrator (xSI) and Calibre 3DSTACK from Siemens EDA. The xSI platform allows for the definition and consolidation of design data. 3DSTACK can then undertake the integrated DRC/LVS.

The paper focuses on four major aspects of this process: Module Verification, Co-design Verification, Logical Verification and Physical Verification.

“Fabless semiconductor and systems industry companies are turning to high density advanced packaging in order to provide more reliable, higher density devices to offset the slowing limitation of monolithic SoC implementations,” argues author. “As companies transition to high density advanced packaging and module design, the importance of a proven, standardized sign-off tool for electrical and physical validation is paramount.”

‘System-in-Package/Module Assembly Verification’ is available for download here.