Zero ASIC open sources system simulation/emulation platform

Open-source hardware and chiplet start-up Zero ASIC has released Switchboard, a combined RTL simulation, FPGA emulation, Python, and C++ communication platform for the analysis of large chiplet-based system designs – and ultimately their low-cost specification.

Switchboard (its open-source Github repository can be found here) targets increasingly common distributed, multidisciplinary designs.

“The framework was designed with performance in mind, using shared memory queues as the underlying communication mechanism,” a company statement says. “Any number of connections can be active simultaneously, each up to 1GB/s bandwidth / 200ns latency. This is fast enough to support real-time interaction with a distributed simulation of chiplets on an active silicon interposer.”

In addition to the open source framework, Zero ASIC has posted an online Switchboard-based emulator with which potential users can experiment.

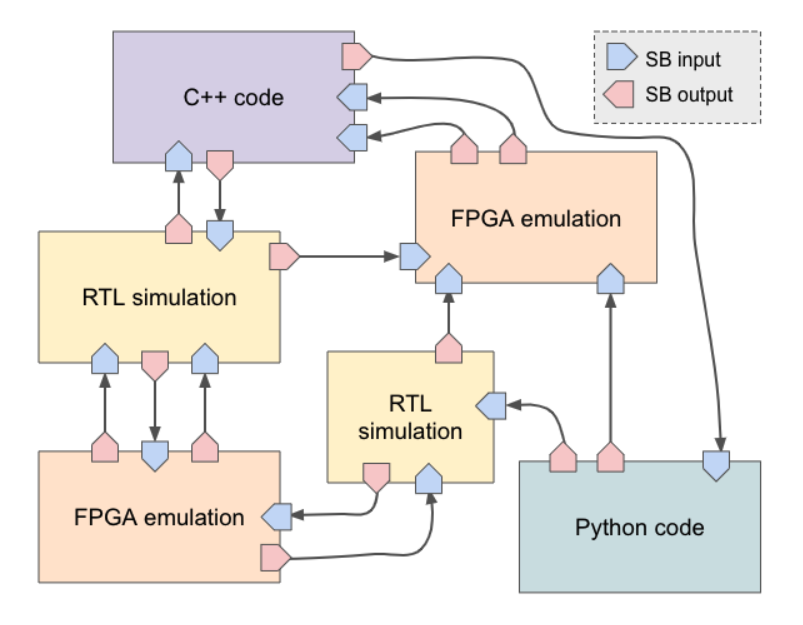

Switchboard has been designed to interface with FPGA cards that represent part of a proposed system. The company provides further support for Python and C++ to enable hardware/software co-simulation. A block diagram of the platform is shown in Figure 1.

Moving beyond simulation and emulation, Zero ASIC ultimately aims to offer composable ASICs leveraging its design platform and chiplet IP and using its initial tools like Switchboard as infrastructure. The company expects its first ASICs to be available from the fourth quarter of 2024.

Andreas Olofsson, CEO and founder, has explained, “Custom Application Specific Integrated Circuits offer 10-100X cost and energy advantage over commercial off the shelf devices, but the enormous development cost makes ASICs non-viable for most applications.

“To build the next wave of world changing silicon devices, we need to reduce the barrier to ASICs by orders of magnitude. Our mission at Zero ASIC is to make ordering an ASIC as easy as ordering catalog parts from an electronics distributor.”

The company launched an also open-source cloud-based complier, SiliconCompiler, late last year.