How MaxLinear cut physical verification time with in-design DRC

A recently published case study describes how RF and AMS specialist MaxLinear cut physical verification time for a complex server DSP by using design rule checks (DRC) integrated within place and route.

The company used the on-demand feedback features within Calibre RealTime Digital from Siemens Digital Industries Software to achieve correct-by-construction results, minimize DRC interations and reduce both cost and time-to-market.

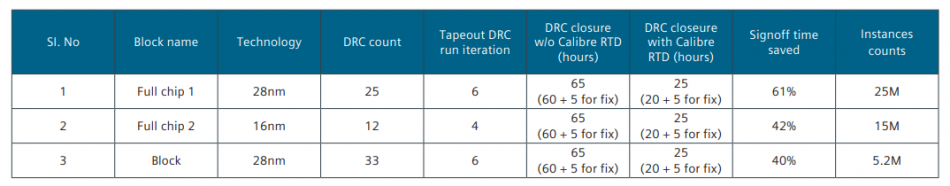

“The Calibre RealTime Digital interface provides direct calls to Calibre analysis engines running foundry-qualified signoff Calibre rule decks (Figure 1). These engines perform fast, incremental checking near shapes being edited, providing nearly instantaneous feedback on DRC violations,” the paper explains.

“This immediate feedback in the P&R domain enables MaxLinear engineers to implement and check fixes with signoff quality, but without the need for full DRC iterations.”

Figure 1. Traditional P&R DRC flow compared to the Calibre RealTime Digital in-design signoff DRC flow (Siemens – click to enlarge).

DRC priorities during P&R

MaxLinear wanted to monitor three areas in particular during the P&R implementation.

Via selection: With a target 80-per-cent via score, MaxLinear’s engineers wanted immediate feedback on the benefits or problems caused by swapping in and out different via types (multi-cut, via bar, single-cut).

Multi-patterning violations: As well as having on impact on the via score, swaps can also cause multi-patterning errors that benefit from in-design analysis, and are best caught early in the flow.

Last-mile DRC closure: Current process node shrinks see cells reduce in size to a greater degree than wires, and the resulting rise in pin density can make it hard for P&R engines to access those pins without incurring DRC errors. Analysis is equally important here as is rapid in-design feedback on any manual fixes that are applied.

Results

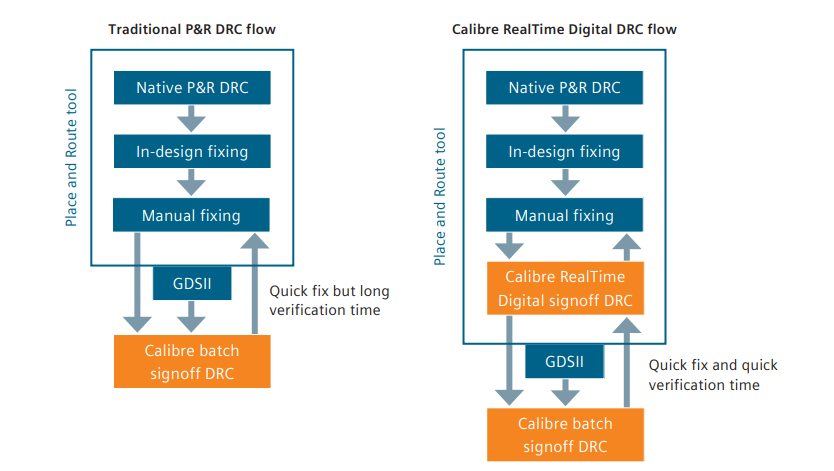

By moving to an on-demand signoff approach that also observed MaxLinear’s specific design challenges and constraints, the designers were able “to save 50% over the previous physical verification closure time required for every design iteration across established and advanced process nodes”, according to the flow and results (Figure 2 – enlargeable) described in the paper.