Synopsys speeds HAPS prototyping with ProtoCompiler

Synopsys has introduced a dedicated software suite for its HAPS FPGA-based prototyping systems. The ProtoCompiler – available in versions for both smaller and larger target designs – brings together a ‘best of’ in capabilities from separate tools such as Siloti, Certify and Synplify for prototype partitioning, compilation, debug and more.

For the first time, transactor resources that were previously sold separately are also bundled within ProtoCompiler. “The further ability to connect the prototype to a workstation running a model or a C++ API adds a lot of value as well,” said Troy Scott, product marketing manager for FPGA-based prototyping tools.

“You can go beyond traditional prototyping tools and, for example, far more closely blend in test benches. This all opens the door to more valid scenarios.”

The key however is addressing some of the major roadblocks on larger designs – those toward 250 million gates and above.

Automated partitioning – based on an informed knowledge of the Xilinx Virtex-7-based HAPS boards will, Scott says, cut runtimes here from hours to minutes.

“Another major bottleneck has been getting the right timeshare configurations on the FPGA pins for the interconnect,” Scott said. “We’ve been able to add a proprietary pin multiplexing scheme for that which gives about a 2X increase in performance.

Also, the system is designed to have enough capacity to captures seconds of trace data for superior debug visibility

Externally, ProtoCompiler is also integrated with Xilinx’s Vivado place and route technology.

ProtoCompiler is available immediately. A variant more suited to smaller designs is provided with HAPS-DX prototyping systems and the full suite is provided for HAPS-70 systems.

“The full release really aims at the needs of multi-FPGA systems,” said Scott,” and we’re seeing a lot more of those all the time. But this is also about reaching out to a much wider market.

“For today’s designs, a low-cost evaluation board can look good, at first sight, but these aren’t really built for advanced prototyping. Certainly though, these configurations won’t be enough for, say, a large GPU or full SoC validation.”

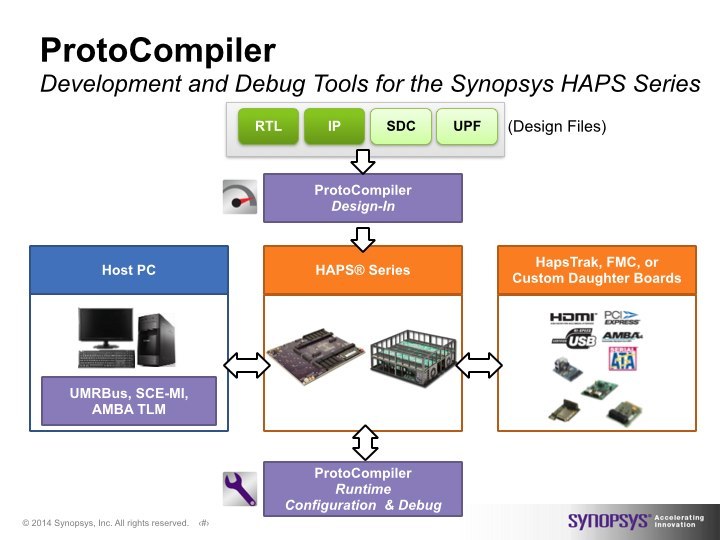

The following graphic shows how the various components within ProtoCompiler fit together to provide a more integrated FPGA-based prototyping flow.