Synopsys extends FPGA-based prototyping to 1.6bn ASIC gates

Synopsys has updated its HAPS FPGA-based ASIC and SoC prototyping system by introducing the HAPS-80 architecture and a related ProtoCompiler software upgrade. It says the combination can deliver up to 100MHz clock speeds for designs that cross multiple FPGAs, or up to 30MHz for designs that need to multiplex signals between them. Designs prototyped within a single FPGA can be clocked at up to 300MHz.

HAPS-80 uses Xilinx’ Virtex UltraScale VU440 devices, which are 2.2 times denser and have 21% more I/O than previous UltraScale devices, so that a single FPGA can accommodate up to 26 million ASIC gates. The HAPS-80 architecture will scale to designs of up to 1.6 billion ASIC gates, and uses a new approach to the high-speed time-domain multiplexing (HSTDM) of signals between the FPGAs.

Synopsys says the performance of the HAPS-80 system enables OS booting to the command prompt in less than a minute, enabling designers to probe and initialize device hardware such as CPU, timers and UARTs. HAPS-80 also enables at-speed operation of real-world I/O.

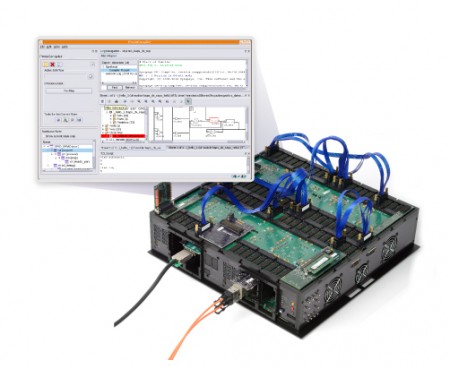

Figure 1 Synopsys HAPS-80system and ProtoCompiler (Source: Synopsys)

ProtoCompiler, which knows about the HAPS architecture and automates the partitioning of the design among the FPGAs, has been updated to take advantage of the new HSTDM capabilities, and so can choose an optimal mix of pin-multiplexing schemes to accommodate the design under test.

ProtoCompiler allows users to manage prototype board resources, enable debug, partition logic, and synthesize a design’s RTL into an FPGA image, to enable the creation of prototypes with optimum multi-FPGA design partitioning, lowest pin-multiplexing ratios, optimized synthesis and guided FPGA place and route.

ProtoCompiler’s hierarchical IP-to-SoC flow encapsulates RTL, design prototyping constraints, pre-defined debug visibility access points and synthesis directives, eliminating the need to replicate these tasks in an SoC and so reducing integration time.

HAPS-80 systems use what Synopsys calls HAPS Deep Trace Debug Gen4 to enable more than 1000 debug signal bits to be captured per FPGA at speed. Debug data acquisition, debug storage memory and dedicated debug routes are automatically inserted by ProtoCompiler to ensure minimally invasive debug is always available to the user. The deep trace debug facility, used with Synopsys’ Verdi debug software, means designers can rapidly visualize complex design behavior in the context of the original RTL source for a simulator-like experience.

The HAPS architecture and ProtoCompiler software use what Synopsys calls its Verification Continuum Unified Compile technology, to ease migration between Synopsys VCS simulation, ZeBu emulation and HAPS prototyping.

HAPS-80 implements Synopsys’ Universal Multi-Resource Bus (UMRBus) to connect to host computers, which enables the system to be used for hybrid prototyping, and as part of a prototyping farm. The UMRBus enables connection between host computers and designs under test at up to 400Mbyte/s.

UMRBus can connect HAPS-80 systems to Synopsys’ Virtualizer-based virtual prototypes, to create an integrated hybrid-prototyping environment for early software development and hardware/software integration.

HAPS-80 has a native Ethernet connection to enable global system accessibility over standard networks. HAPS-80 and ProtoCompiler can be used to execute multiple designs simultaneously across HAPS systems in an enterprise configuration, to improve the utilization of a prototyping server farm and so increase the return on investment. Multi-design capabilities include: client/server system configuration software; remote access; multi-design support; and job queuing.

HAPS-80 is backward compatible with HAPS-70, and interoperable and compatible with HapsTrak 3/MGB accessory equipment to support the assembly of multiple prototype projects.