Synopsys strengthens analog and mixed-signal verification with VCS AMS

Synopsys has launched an initiative to speed up the verification of mixed-signal ICs through faster simulation, better regression techniques and new AMS testbenches. The announcement comes a couple of weeks after Synopsys’s launch of Verification Compiler, an effort to speed up the verification of digital ICs.

Steve Smith, senior marketing director for AMS verification at Synopsys, drew a parallel between the evolution of verification for digital ICs, which has gained from the introduction of compiled Verilog simulators, constrained random testing and System Verilog-based methodologies, and what has to happen in order to verify today’s AMS designs quickly.

“It’s time to introduce a more sophisticated verification approach, adding MS regression to overall verification,” he said. “Analog functions are much more sensitive to on-chip variation and so you need to analyse hundreds of process corners. Because of this, auto makers want a System Verilog-like approach to AMS verification.”

The first step towards this is better integration between VCS and the CustomSim FastSpice simulator. The two simulators can already interact, and in June Synopsys will launch a unified version of the product.

One of the keys to AMS verification is ensuring that the analog simulator is fast enough to keep up with what is happening on the digital side of the design. This is, in part, a function of the relative complexity of the analog and digital portions of the design – Smith says the current approach will work best for ‘big D, little a’ designs. CustomSim FastSpice, the analog simulator, has been under continual development to improve its performance, with the latest multicore version offering speed-ups of anything between 3.5 and 6.6x, depending on the number of cores employed and the nature of the target design.

The next part of the initiative is to improve AMS testbenches, in part by extending UVM, the Universal Verification Methodology, with utilities to enable testbenches developed for digital blocks to be reused when those blocks become part of an AMS design. This takes a series of steps:

- Managing the conversion of signals between electrical and real representations at the interfaces between analog and digital blocks

- Handling asynchronous events passed from the analog to the digital domain

Other enhancements include:

- Support for shaped-source voltage generators

- Developing ways to handle a suite of measurement techniques, such as:

- AMS assertions and checkers

- AMS constrained random stimulus

- AMS checkers

- Support for real number modeling in System Verilog

- Reference model integration at multiple abstraction levels

- Using self checking for AMS testbenches, source generators and functional coverage

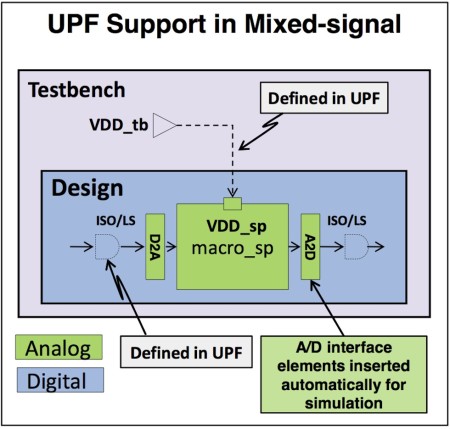

Another important part of the new AMS strategy is supporting the verification of low-power AMS designs. According to Smith, VCS already incorporates a multi-voltage simulator that mimics a multi-voltage environment within a digital simulator. With VCS AMS, Synopsys has taken another step by using UPF, the Universal Power Format, to enable designers to specify how voltage levels will be translated across analog/digital boundaries. The tool then automatically inserts the necessary converters between domains, so that Spice elements of the design appear as digital blocks to UPF.

Figure 1 UPF lets designers specify how voltage levels translate across analog/digital boundaries (Source: Synopsys)

One of the non-technical challenges of accelerating the verification of AMS designs may be getting designers to use the new techniques. For some analog designers, even representing their designs as behavioral models as well as schematics may be new. Adding in the use of concepts from the digital world such as assertions and checkers will take further collaboration and shared learning – which is beginning to happen.

“We are starting to see analog designers, digital designers and verification engineers all talking in the same place,” said Smith.

Availability

VCS AMS should be available in the second quarter of the year.