Intel foundry to make Altera FPGAs

The Intel foundry business will make FPGAs for Altera on a future 14nm tri-gate finFET process.

John Daane, president, CEO and chairman of Altera, said: “Altera’s FPGAs using Intel 14 nm technology will enable customers to design with the most advanced, highest-performing FPGAs in the industry. In addition, Altera gains a tremendous competitive advantage at the high end in that we are the only major FPGA company with access to this technology.”

Altera said the process would be used to make ultra high-performance systems for military, wireline communications, cloud networking, and compute and storage applications.

Brian Krzanich, chief operating officer, Intel, said: “We look forward to collaborating with Altera on manufacturing leading-edge FPGAs, leveraging Intel’s leadership in process technology. Next-generation products from Altera require the highest performance and most power-efficient technology available, and Intel is well positioned to provide the most advanced offerings.”

Intel foundry

Intel has been exploring the foundry business model again recently, building chips for starts-ups including FPGA makers Achronix Semiconductor and Tabula, which said in December that it was close to taping out a part on Intel’s 22nm finFET process.

The move to take on work for Altera represents a step up in Intel’s commitment to its foundry business, taking on a major company in a key, high-performance market, that needs Intel to deliver over the long term in order to sustain its product roadmap. The move will also rebalance things in the FPGA market, bringing Intel’s process technology head to head with TSMC, foundry for Xilinx.

Previous efforts by Intel to enter the foundry business have usually foundered (sic) on its need to protect the processor business when manufacturing volumes got tight or the political winds within the company changed. Daane seems sanguine about Intel’s commitment, though, telling Reuters: “We are essentially getting access like an extra division of Intel. As soon as they’re making the technology available to their various groups to do design work, we’re getting the same.”

More performance

Altera has clearly been casting around for a way to achieve greater performance for its FPGAs for a while. At a meeting held by the SOI Industry Consortium at the International Electron Devices Meeting in San Francisco last December, Jeff Watt, technology development Fellow at Altera, discussed experiments he had been doing to assess the value of FD-SOI for FPGAs, using models for a 28nm FD-SOI process, provided by the SOI Consortium and backed by experimental silicon results from IBM.

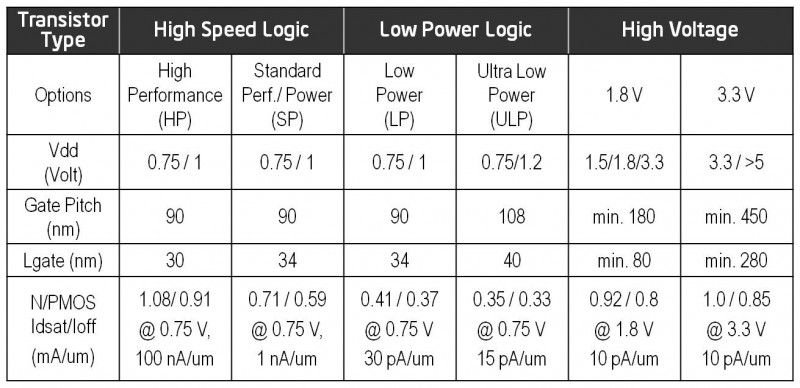

He said one aspect where the two fit well is in supporting Altera’s ‘programmable power technology’ strategy, which uses body biasing to adjust the power/performance trade-off of the process to match the local needs of the user’s design. Although this approach won’t be directly replicable in the Intel process, the semiconductor giant used the same conference to emphasise the flexibility of the SoC process it has developed as a superset of its 22nm microprocessor manufacturing process, particularly its ability to tailor transistors to deliver high performance, ultra-low power or high voltages.

Meanwhile, of course, TSMC hasn’t been resting on its laurels, declaring that it will put a 16nm finFET process into risk production by the end of this year.