Case study demonstrates 59% extra power savings for HPC

A newly published case study describes how a Taiwanese consultancy used novel clock tree synthesis (CTS) in conjunction with Mentor’s PowerPro RTL platform to lower dynamic power consumption on an ASIC project by 59% against the use of traditional techniques.

Alchip was working on an ASIC for a high performance computing (HPC) client. The design targeted a 16nm process with a core processor in a 24×24 array structure at a clock frequency of 600MHz.

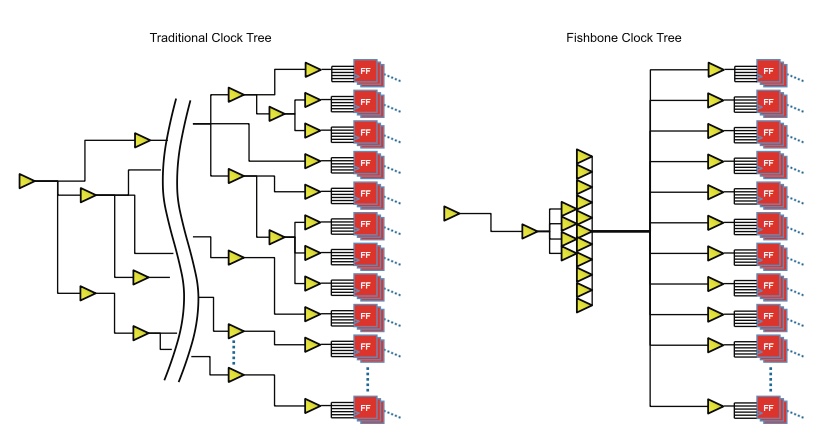

The company coupled the use of Mentor’s PowerPro suite to that of a fishbone clock design methodology for CTS. This strategy “balances the stage count from the root to all the flip-flps by employing multi-drivers in a pattern that resembles the bones within a fish” (see Figures 1a & 1b).

Sequential clock gating for low power design

Alchip then leveraged a number of features within PowerPro. These included:

- automated sequential clock gating (an expert engineer has previously been needed to carry out the necessary analysis); and

- optimized memory gating to remove redundant memory accesses (using both observability-based read gating and stability-based read gating).

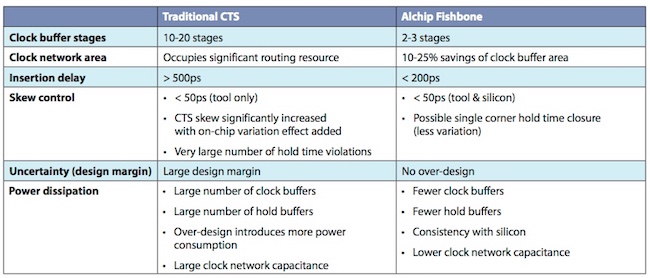

The red ticks in Figure 2 show additional gating that was inserted by PowerPro based on observability.

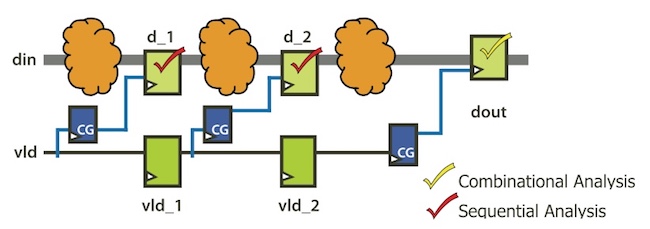

The red ticks in Figure 3 show additional gating that was inserted by PowerPro based on stability.

The tool specifically helped Alchip to reduce flip-flop power by 26% and memory power by 80%. Coupled with the fishbone CTS approach, these techniques produced the overall 59% improvement in low power optimization.

The company now plans to take PowerPro to future HPC designs targeting the 7nm node.

Alchip Minimizes Dynamic Power for High Performance Computing ASICs is available for immediate download.