‘Known unknowns’ and the Cadence take on verification IP

We have Donald Rumsfeld, the former US defense secretary, to thank for the wonderful phrase ‘Known unknowns’. In some quarters, it has become a useful mid-point between ‘Complete ignorance’ and ‘Yeah, I think I get that’. But could it also become a valuable concept for system design? Accept that there are some things that you don’t know, that you’ve never known and that you never will know – because you don’t have to. Right now, the idea appeals specifically in terms of verification IP.

We recently got the chance to sit down with Susan Peterson, group director for Verification IP product marketing at Cadence Design Systems, and she does see one strongly related trend developing, even among the biggest players.

“To some extent, we used to think our job was to help people to verify a protocol, but now it’s now also about helping them to understand the protocol. In the past, we assumed that they would come to us with much of that understanding already,” she says.

“Today, right through to our documentation and our user interface, we build more and more of a knowledge base in the products themselves. So, where there are maybe three choices, it’s part of our tool’s job to say, ‘If you choose option one, it means this. If you choose option two, it means that. And option three means something else again.’ Even a couple of years ago that wasn’t the assumption.”

Verification IP gets smarter

It isn’t that system design companies have become lazy. It may not even be a result of the tighter resources everyone has to work with at the moment, though that will often apply. It’s more that the IP itself is becoming harder to implement.

Each discrete block of IP is becoming more complex, a consequence of increasing product functionality and also the shift to multicore. Then, there’s simply so much more IP out there. And, at some point, it all has to be verified.

“One example of how difficult the protocols are getting is ACE. It’s the cache coherency extension to [ARM’s] AMBA4,” says Peterson. “You can see why you need it for multicore but it comes with a massive amount of documentation and it is very hard to verify.”

She might well cite ACE. Cadence just unveiled some verification IP work it did on ACE with Hisilicon, the Huawei chip design subsidiary. A big well-resourced player with aggressive plans as an innovator turned to Peterson’s company to reduce its verification effort and get an inside track to help customize the ARM technology.

Then, though, there is proliferation. Since last year, Peterson’s presentations have included a useful foil that tracks just the most recent verification IP additions in the mobile space (it’s one of the main graphics in our verification IP guide). AMBA has been and remains busy. But now consider the MIPI Aliiance, which provides IP to connect and add functionality to those devices. Its family has mushroomed.

“MIPI is still going like crazy. There’s CSI-3 [the third generation camera interface]. There’s DSI-2 [the second generation camera interface]. And then there’s PCI Express over [MIPI] mPHY and SSIC over mPHY,” she says.”On top of that, HDMI 2.0 comes out in December. And of course, there’s USB doing new things in power delivery and all the other ‘established’ groups.”

Indeed, in referring to more established IP families, Peterson now also has this related tracker for verification IP activity in cloud computing. An inevitable domino effect is being driven by mobile designers looking to offload much of what the device in your hand might do into the cloud.

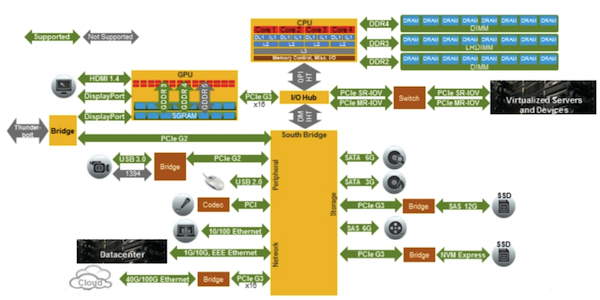

Figure 1

Cadence cloud infrastructure verification IP suite – server, networking and storage (Source: Cadence Design Systems – click image to enlarge)

There is quite simply too much for most design companies to handle internally. Even where many of them are actively driving standards – MIPI has players such as ARM, Intel, Nokia, Samsung, STMicroelectronics and Texas Instruments behind it – they are wooing the verification IP vendors to join their alliances because of their expertise in verification. In short, it’s being left to the experts.

and time to market… of course

“Though it is also about real hard time-to-market pressure as well as the amount of IP you might be trying to manage,” Peterson says. “If you miss Christmas, or Diwali, or Chinese New Year or even just ‘back-to-school’, that can cost you millions of dollars. And now, a lot of the buying is done by – well, for – your 15 year-old or even your five year-old, and they’ve got a lot less tolerance for something that doesn’t quite do it.

“For example, about a year and a half ago, we had a customer who wanted to make sure that LP DDR3 was in their next device. And they wanted it to be out in time for back-to-school. All of a sudden, my memory model was in a critical path for them to hit that deadline. At the same time, it was worth a lot more to them than it had been in the past.”

From the sound of that, Verification IP is currently a good business to be in. Hit the quality standards and have the VIP ready as the specification comes out (or as near to as possible) and you take away a lot of customers’ headaches.

And another area where Cadence has been picking up some kudos is for accelerated verification IP, which can run hundreds of times faster than traditional RTL simulation. It’s a good fit for validation and also driver and firmware integration.

“When you get to the large system or subsystem, simulation does run out of steam if you’ve got a whole bunch of stuff tied together. So being able to move into acceleration without throwing your whole UVM testbench aside really is useful,” Peterson says. “We now have accelerated VIP for AXI, PCI Express, Ethernet, SATA and HDMI and we’re introducing one or two more each quarter. We’re not resting there and we’re building a good strong portfolio.”

That further sign of a growing market brought us to one last question. With its acquisition of Denali, Cadence gave itself hefty verification IP market leadership, with 69% according to recent EDAC numbers. The same survey gave its nearest rival, Synopsys, 25% – but it has embarked on an concerted bid for much more with an all-SystemVerilog strategy.

“It’s good to have that though,” Peterson says. “I’m glad to have Synopsys going hard for this market. It’s like having McDonalds and Burger King across the road from one another. It puts some intensity in the game. and more people talking about the space.

“But it’s driven a lot by real world requirements. There’s more and more need for what we all do.”