March 29, 2024

RISC-V adoption is growing fast as is the ecosystem around the open-source core. Hardware and software are now vital for appropriate debug.

August 8, 2023

We have the technology. Learn how to 'shift left' with Calibre DesignEnhancer and meet IR, EM and PPA objectives.

July 5, 2023

NAND flash is a key technology for all systems. 3D techniques now control its cost and potential for future capacity increases.

February 8, 2023

Moving part of all of a design flow to the cloud involves careful preparation and evaluation as there is no 'one-size-fits-all'.

January 26, 2023

Learn more about the five interconnected workflows that are democratizing next generation design in the emerging chiplet age.

October 19, 2022

Knowledge, intelligence and optimization are key to managing the logistical disruption seen since the Covid-19 outbreak.

January 12, 2022

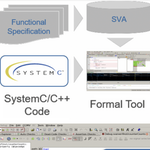

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

October 26, 2020

One roadblock to the integration of IP from multiple vendors into an SoC is the likelihood of finding duplicate cell names in the merged design. Carefully considered renaming strategies can fix the problem without causing design database bloat.

May 29, 2020

The promise of autonomous vehicles is driving profound changes in the design and testing of automotive ICs.

September 18, 2019

A look at the complexiites of implementing a Bluetooth Low Eenergy interface in an SoC.