February 8, 2024

Take a high level view of the AI strategies used within the Tessent family to improve across-the-board performance.

March 22, 2021

SLS brings the power of product lifecycle management to the increasingly complex oversight challenges in electronic systems design.

July 9, 2018

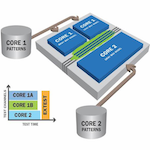

A hierarchical methodology removes DFT from the critical path for large designs. The methodology is compatible with other techniques such as channel sharing, which can further reduce ATPG turn-around time and test cost.

September 21, 2017

Diagnosis-driven yield analysis identifies the cause of systematic yield loss to speed the ramp-to-volume on new processes and improve yield on mature ones.

January 10, 2017

How a new software-led flow speeds silicon bring-up within the Tessent environment, including a Cypress Semiconductor case study.