Analyzing common resistance to deliver design reliability

Full-chip parasitic extraction was once the default tool for analyzing the impact of interconnect resistance on design reliability at both the physical and operational levels. But, as is so often the case, increasing design complexity and size is creating a need for more targeted approaches.

Common resistance – that determined by the pre-branched segments of a net from a given starting point (Figure 1) – is one such area. Particularly for analog design, this factor has an impact on noise, voltage drop and electrostatic discharge – the last of those being a reliability check that many foundries consider a prerequisite.

Figure 1. Diagrams showing (a) a common segment topology for a net connecting a pad with multiple blocks; (b) a common resistance segment highlighted in a layout (Mentor)

A recently published whitepaper, ‘Net common resistance extraction is crucial to design reliability‘, describes how checks across these important areas have been automated within the Calibre PERC reliability platform.

It contains pre-coded, packaged checks for common resistance and a topology engine that looks at point-to-point resistance and current density interconnect resistance extraction.

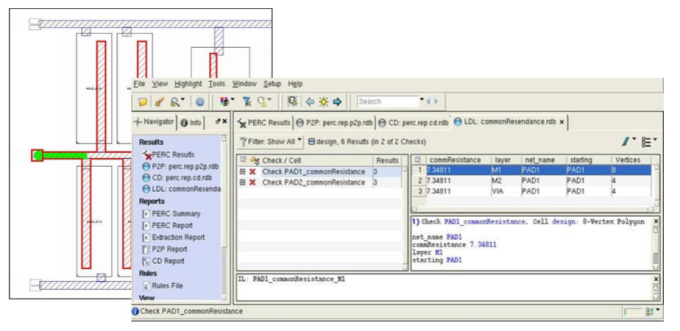

Figure 2. Results from a common resistance check highlighted in Calibre DESIGNrev and RVE interfaces (Mentor)

The results are available for data-led and visual review and can then be passed on to augment further checks within Calibre (Figure 2).