Catching complex CDC bugs in large SoCs

Much of the complexity of large SoC designs is due to the many signals that integrate the IP blocks into a cohesive whole – clocks, resets, and power-management signals. These present a verification challenge because they are often asynchronous to other parts of the design, and can cross in and out of clock, power and reset domains, leading to potential metastability issues that are hard to find and hard to fix.

One way forward is to use a variety of static verification techniques to ‘divide and conquer’ the

issue, according to Kiran Vittal, director product marketing, and Sean O’Donohue, senior corporate application engineer in the verification group of Synopsys, in an upcoming webinar.

Synopsys offers a suite of RTL sign-off tools under the SpyGlass brand, including linters, CDC and reset domain-crossing tools; constraint (SDC) checkers; power estimation, reduction and verification; and DFT testability checkers. Vittal and O’Donohue will argue that applying these checks when the design is at the RTL level can reduce iterations at both the IP integration and implementation phases of the process.

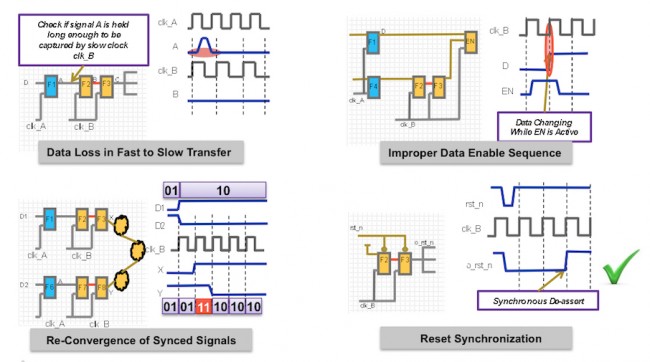

The webinar will include an overview of the CDC challenge, including a look at some of the typical issues that it can cause, as shown in Figure 1.

Figure 1 Some typical bugs cause by CDC issues (Source: Synopsys)

The first issue shown is data loss in fast-to-slow transfers, which happens when two clocks are of different frequencies and the data launched by a fast clock is not captured by the slower clock.

The second is improper data-enable sequencing. This can happen if the data changes very close to an Enable signal change, even if the Enable is synchronized with a double-flop sync scheme, and causes a data hold issue.

The third, which the speakers say is the most common chip killer, involves the re-convergence of synchronized signals.

The fourth issue illustrated is with reset synchronization schemes, and especially situations in which multiple reset domains have been created.

The webinar will discuss techniques to address these issues, using SpyGlass tools, including in hierarchical (top-down or bottom-up) approaches, as well as in power-managed designs.

Vittal and O’Donohue will also discuss reset-domain crossing challenges, including the introduction of metastability issues when reset signals become asynchronous.

The webinar will also describe a methodology at both RTL and gate level netlist to ensure that SoCs do not suffer from any CDC violations.

There’s also a brief look at the way some of these techniques can be applied to FPGA-based designs, including those being developed under the DO-254 methodology guide for military and aerospace uses.

You can register for the upcoming January 26 webinar here.