Mentor targets next-gen Ethernet with emulation

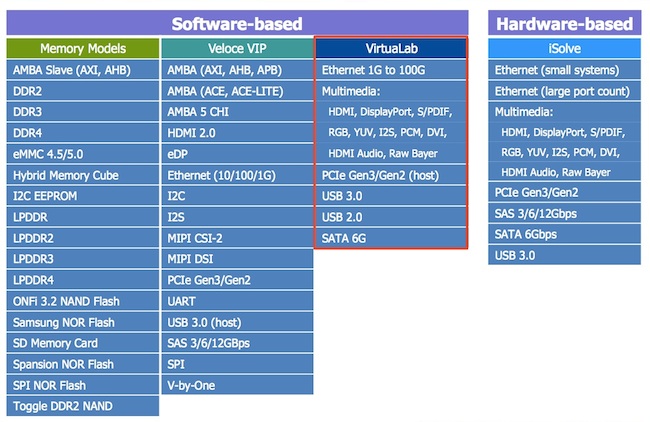

Mentor Graphics is today (October 19) launching support for 25G, 50G and 100G Ethernet within its Veloce VirtuaLAB emulation offering.

According to Jean-Marie Brunet, Mentor’s Director of Marketing for its Emulation Division, the move reflects both the increasing demands on comms silicon developers and the ongoing shift from lab-based in-circuit emulation (ICE) to the virtualized, transactor-based verification offered by VirtuaLAB.

Today’s networking chips can easily exceed 140 million gates with methodologies scalable to one billion gates a near-term requirement, one specifically targeted by this week’s launch.

The cloud as well as other emerging technologies and markets have put this capacity demand on the agenda. Simulation is already too slow and ICE is not merely reaching the limits of its scaleability, but also cannot provide the kind of multi-team and multi-site emulator access such complexity demands.

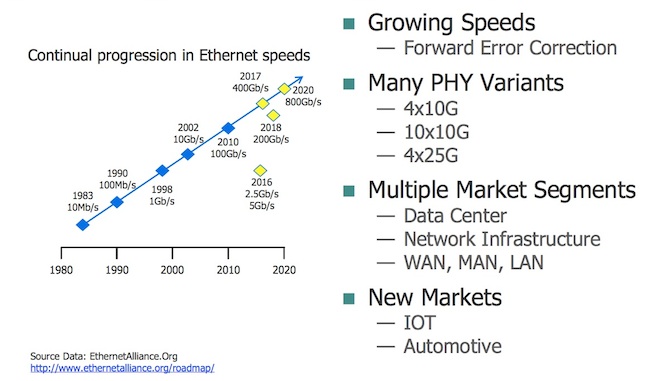

In particular, networking today requires early hardware and software verification and validation. There are also the Ethernet technology challenges of forward error correction and multiple physical layer variants to consider.

Mentor and rival emulation providers have been promoting the benefits of virtualization hard for several years. Once upon a time, emulators were expensive ‘secrets’, closely guarded by lab engineers. By moving their use out of the lab and into datacenters, emulation companies have not only broadened use-cases but also made it easier for engineering managers to make the ROI case for investment.

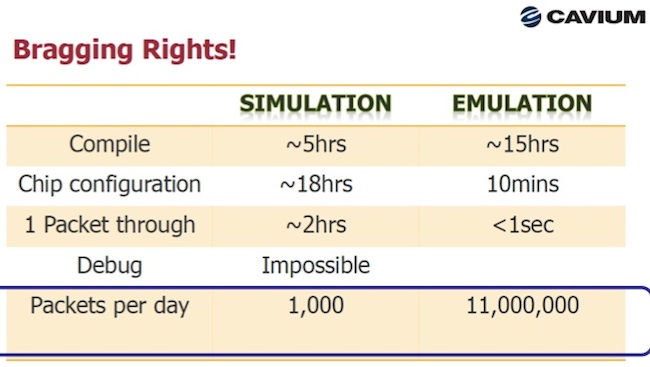

The VirtuaLAB components Mentor is now announcing are based around a complete software-driven Ethernet stack that runs at up to 15,000 times the speed of simulators. Fabless comms chip expert Cavium recently published data on its experiences using virtualization with Veloce that show chip configuration in 10 minutes and a run-rate of 11 million packets a day during a verification project.

VirtuaLAB components are software-based, full applications for the verification of complex SoCs that obviate the need for external hardware. Apart from networking, Mentor has been building out a broad portfolio of similar tools across areas such as multimedia, PCI-Express, USB and SATA.

The company also offers VIP, memory models and hardware-based iSolve solutions for its Veloce emulator family.