Hardware verification puts software first

The expansion of the Veloce hardware-assisted verification family at Siemens EDA says much about the division’s evolution and future direction, following its acquisition as Mentor Graphics.

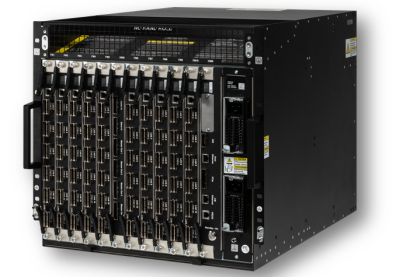

At the most basic level, there is the power of Siemens’ checkbook. This has allowed the investment needed to deliver an on-time upgrade to the main Veloce Strato emulator itself – the Strato Plus is powered by a new 2.5D Crystal3+ custom device, making it faster and lifting capacity to 15 billion gates from 10 billion. It has also allowed the company to move into FPGA prototyping via an own-brand enterprise product, Veloce Primo, as well as offering a desktop option via an OEM agreement.

We have been seeing this for a while though in the form of acquisitions – the latest being OneSpin Solutions in formal verification – as well as new product launches. But the Veloce announcement also reflects an idea the company began to promote last year: “Software performance defines semiconductor success.”

As described by Jean-Marie Brunet, Senior Director of Product Management and Engineering for the Scalable Verification Solutions Division, an overarching objective for Veloce is allowing users to, according to the stage of a project, “use the right tool for the right task because not all steps [in a flow] are equal in their needs and requirements.”

In a great many cases, that task involves achieving the greatest amount of software verification and validation that the maturity of the hardware RTL will allow, alongside ‘traditional’ work and, increasingly, as early as possible.

Hardcore emulation for software

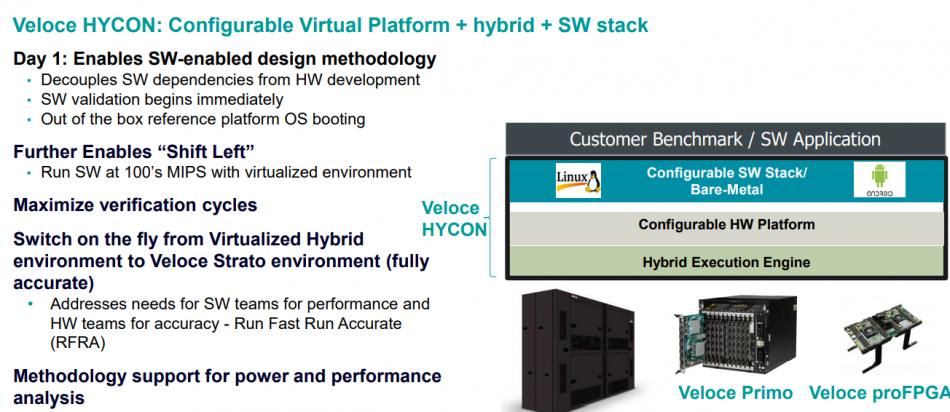

To this end, the other important new addition to the family is Veloce Hycon (Figure 2), which specifically targets early-stage software-oriented verification. Simply performing this kind of work in a virtualized environment is not so new in itself; the important aspect of what is possible in Hycon and further along a Veloce flow is that the configurations are both consistent and interchangeable.

In simple terms this can allow verification and validation to switch back and forth between a faster virtualized environment and the slower one necessary for full RTL verification hardware as a project matures. Want to choose the best configuration whether your immediate focus is hardware or software with the RTL 20%, 40% or more in place? Off you go.

At some stages, the verification team will need greater visibility for debug. That work traditionally favors the Veloce emulator. At others though, you may want the greater performance of an FPGA prototyping platform – either in an enterprise/rack configuration with Primo (Figure 3) or on the desk for ICE examination with proFPGA. And if, having gone to FPGA and discovered that a bug persists, you may want to go back to emulation.

Figure 3. Veloce Primo takes Siemens EDA into FPGA prototyping at the enterprise level (Siemens EDA)

There is, then, a lot of power in the ‘special sauce’: the models for virtualization that allow not only earlier validation but also confident moves between different environments; and the compiler that integrates what you analyze on the different platforms.

Beyond all this another aspect of the deal is worth noting. Mentor was never simply a point-tools company, but it was one noted for particular strengths and the ability to focus on them tightly – high-level synthesis and design for manufacturing immediately spring to mind alongside its earlier work in verification.

Under Siemens, there has been a move toward more of a ‘one-stop shop’ approach. The presentation for the Veloce expansion specifically notes, “We have it all.” Yes, deeper pockets make for a broader offering, but with the degree of virtualization involved here, the company’s wider ambitions in the development of fully-featured digital twins and their hooks into the real world is similarly made clear once more.