Aprisa team to be doubled after Mentor purchase

Mentor, a Siemens business, plans to expand the team working on the Aprisa place-and-route tool following the purchase of Avatar Integrated Systems, announced in July.

Joe Sawicki, executive vice president for IC EDA at Mentor, pointed to the work performed by what was a relatively small team at Avatar in putting together and maintaining a place-and-route engine over more than half a decade amid massive changes in process technology, with a growing emphasis on the use of design optimizations to deliver density improvements.

“When they came to us and said, ‘We have something important’, I have to admit we were somewhat skeptical. But when we did some benchmarks, what it could do absolutely stunned us,” Sawicki said. “Whether it was 16nm or 7nm, they had very competitive results. They were easily in the ballpark of the leading technology out there, and that was with a small team.”

Sawicki said one important element of the architecture of the tool is its use of a single data model. “All the competitors talk about how they use a common data model. But this is a true single data model that lets the tool be more efficient. A second factor is that it has always been routing-centric.”

Route-centric approach

The issue for most other tools, said Sawicki, is that they have focused primarily on placement and organizing a closer connection between synthesis and placement to try to minimize distance between closely linked cells and, with that, cut delays. The problem in advanced nodes is that limited pin access, which has been exacerbated by a move to lower track counts and fewer connection points within cells, has a dramatic effect on routability between those cells. In order to make the connections, the tool may have to swap cells around and space them out, killing the utilization ratio in the process, as well as making use of many more vias that increase overall resistance. “Routing has become the key issue,” he argued.

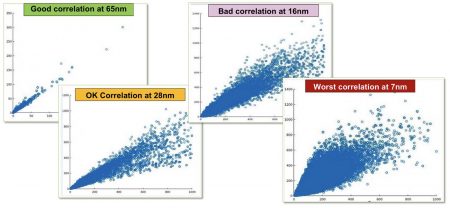

Image Pre- vs post-route delay correlation for successive process nodes

Sawicki used the correlation between pre-route and post-route delay estimates for successive processes to show how the issue plays out in practice. Correlation has steadily worsened over time with quite poor results for pre-route estimation at 7nm.

One of the ways that Aprisa deals with the problem is to use resynthesis to generate alternative cell options that may give the tool better routing possibilities and, with that, improve utilization and timing. “It became a no-brainer for us to pick it up,” Sawicki claimed.

Bigger team

“Now we will be doubling the size of the team,” he added. To do that, Mentor will move engineers from the company’s existing place-and-route tools teams with the focus on those older tools moving to maintenance. Sawicki said there is future potential to build connections between synthesis and placement but that, because of the demands of the sub-10nm nodes, the main issue to handle is the detailed routing and what that means for resynthesis and layout at that point in the flow.

One potential issue for sub-10nm routing is the increase in the apparent number of nodes as foundries such as TSMC start to push greater use of EUV into the lower interconnect layers is not greatly complicating the effort to do effective place and route. Sawicki pointed out that previously, many of these sub-nodes would simply have had letters appended to them rather than being treated as a full node. But each of them has involved tweaks. Similarly, though foundries in China are having to find ways to push geometries without access to EUV and other more advanced tools, the kinds of design-technology co-optimization techniques they are using will most likely be versions of those already encountered in the development of low track-count cell libraries for the mainstream bleeding-edge nodes.