Tackling IR drop and EM with a push-button via utlility

Moving through process nodes has progressively increased the impact that IR drop and electromigration have on both reliability and yield. At the same time, it has become ever harder to address them by adding vias. Relevant design rules for advanced nodes are now so complex that internal custom scripts used for spacing, count and other factors cannot keep up.

Mentor, a Siemens business, is now automating this work within its Calibre suite. A new technical paper describes the ‘push-button’ Calibre YieldEnhancer PowerVia utility.

With foundry rules built into the software, its automated but customizable flow is claimed to have delivered results such as a 5-10% in both EM and IR drop results after initial manual enhancement and a 68% reduction in current density violations.

The paper describes a core three-step process. The utility:

- Scans the design by net name(s), as defined by the design team.

- Locates candidate locations for via insertion by identifying layer intersections of the same net.

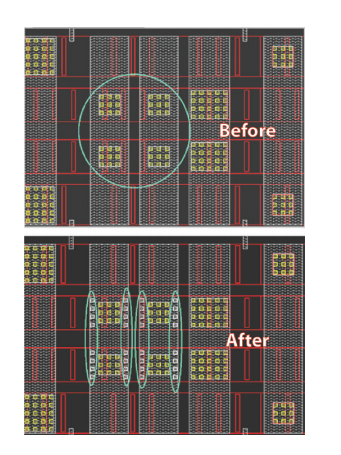

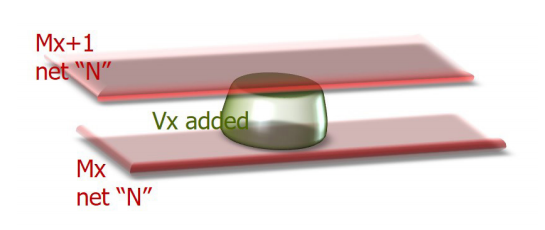

- Uses the foundry requirements, and then inserts as many design rule check/layout versus schematic clean vias as possible at these locations (Figure 1).

“The additional vias are selected based on the type of layers intersection,” the paper says (Figure 2).

‘Reducing IR and EM issues with automated via insertion’ is available for download here.