A repeatable methodology for modern reset domain crossing issues

Reset domain crossing (RDC) is becoming an ever thornier problem as SoC designs grow in size and complexity.

Designs are incorporating an increasing number of intellectual property blocks across which engineers will likely have to manage multiple asynchronous reset domains.

If this task defeats them, designs run the risk of metastability. This can lead to the propagation of unpredictable values to downstream logic, and in turn prevent a device resetting to a known-good state. That last consequence cannot merely result in unreliable start-up – there have been cases where it has led to the overconsumption of power and irreparable damage to the device.

As many of these increasingly complex SoCs target the automotive and aerospace markets – as well as others that set a high bar for safety (e.g., ISO 26262, DO-254) – the need for an approach that masters modern RDC is obvious.

In response, a technical paper has recently been published that describes a ‘specification-driven methodology’ based on a three-step approach to reset domain crossing. It is both systematic and repeatable. To that end, the paper considers the use of the methodology on both an IP block and a broader SoC design for digital networking.

The three stages in the reset domain crossing methodology are:

- RDC design requirements specification and verification plan. Definitions are undertaken with close attention to not just asynchronous clock and reset domains but also reset ordering, RDC clock isolation enables and RDC data isolation enables.

- RDC design and verification. Implementation is described that draws upon appropriate reset staging methods and RDC synchronization methods.

- RDC results progress tracking and completion metrics.“By quantifying the verification tasks, design teams have explicit criteria for completing each step in [a] RDC verification methodology. RDC verification coverage metrics will qualify the verification methodology including the setup, analysis, review, and debug tasks, and these coverage metrics will be correlated to the initial RDC verification plan.”

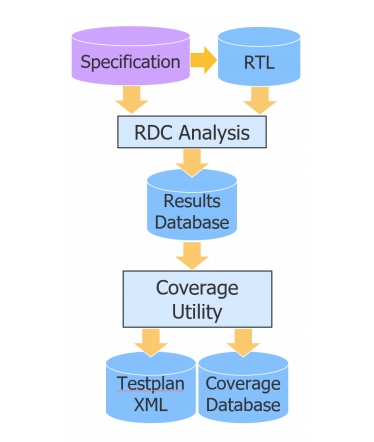

A block diagram overview of the methodology is shown in Figure 1.

‘A Specification-Driven Methodology for Reset Domain Crossing Logic’ can be downloaded in full via this link (registration required).