Automotive complexity drives DFT to the RTL

Automotive electronics and the move toward self-driving vehicles are forcing a rethink of how engineers approach design-for-test (DFT). In particular, they are promoting a need to address DFT at the RTL level and as a system problem; it can no longer wait until the gate level.

The pressures facing automotive design are behind the trend. The technological complexity inherent in delivering fully autonomous Level 5 vehicles that meet the highest ASIL-D safety requirements is the biggest driver. But there are others.

The competitive landscape is changing. IC and systems companies that have operated outside the automotive market are aggressively bidding for a slice of it. For their part, traditional players are seeing existing, necessarily conservative design strategies challenged, even broken by the sharply accelerating rate of innovation.

Meanwhile, scalability is also becoming a major issue. Architectural and methodological decisions taken today must be able to evolve to meet tomorrow’s inevitable challenges. Among them are the challenges posed by the adoption of new process technologies, disruptive (and constantly changing) automotive-specific AI algorithms and ever-shrinking time-to-market.

DFT and the automotive challenge

These challenges apply to any system design process, but test has become a major pressure point for automotive designs specifically.

The IC count in public and private vehicles is set to increase by at least an order of magnitude, and the gate counts of these chips are also mushrooming.

Many new types of automotive IC will feature in safety-critical applications. For example, they will contribute to computer vision tasks that underpin collision avoidance or help to manage the platooning of large trucks.

Alongside all this, increasing performance demands mean that a sector which has historically felt more comfortable designing for mature process nodes is increasingly forced to adopt the latest.

Single-digit targets for the number of defective parts per billion are being set (e.g. Infineon talks of ‘<1 DPPM’). So are demands for more extensive in-system test. Test can take place both before before and after a vehicle goes on the road, and also in an online context where part of the logic is tested periodically.

There is still some way to go. ON Semiconductor recently analyzed one million parts fabricated at 350nm, based on advanced automotive DFT techniques using cell-aware testing, and still encountered 114 DPPM.

As for in-system test (IST), the intense media coverage – traditional and social – that follows any failure of an autonomous vehicle during current road trials reminds us how high the bar is.

So, tension. But thankfully, tool vendors say they have solutions that can already help OEMs and newcomers to tackle things in the right way and at the right time.

Why DFT cannot wait

A number of DFT solutions are helping us alleviate the pressure. There are more powerful fault models (e.g., cell-aware, timing-aware, bridging and stuck-open). Mentor is pioneering a model for AMS fault simulation that addresses a particularly problematic area in terms of defective part rates.

To make these techniques work efficiently and effectively, they need to be brought into play at the RTL, integrating advanced DFT within the design specification. This is because of the safety issues involved, ones that are are so complex and sensitive that they resist being addressed at the gate level. Moreover, the ISO26262 functional safety process demands that these problems are addressed early in terms of analysis, validation and verification.

Consider this strategy for mastering complexity and design schedules through a novel approach to the DFT architecture.

Mentor worked with partners such as Intel, to develop a hybrid DFT architecture that serves both manufacturing test and IST – two areas that have traditionally required separate IPs for ATPG and LBIST.

The work brings together embedded deterministic test (EDT) and LBIST around a single reconfigurable IP that can be inserted at the RTL to save area. This shortens the design cycle and delivers compliance with the automotive development process. The in-system test IP is inserted at the RTL level for the same reasons.

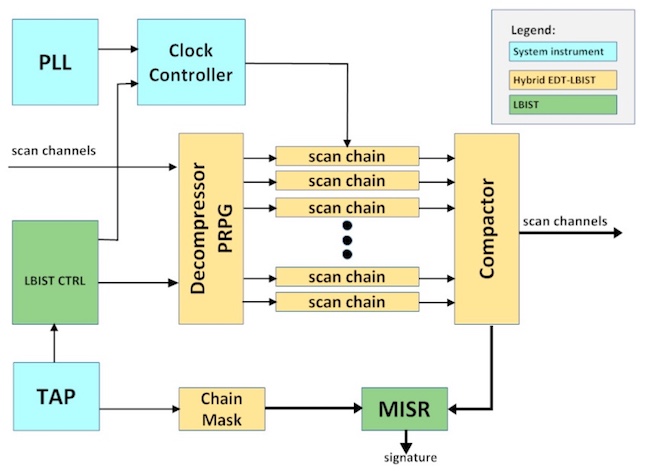

It was described in a recent paper* from the International Workshop on Automotive Reliability and Test (ART). A block diagram of this architecture is shown in Figure 1. The gold blocks are those required for standard EDT. The green blocks are those that were added specifically for LBIST.

According to the paper, the architecture provides very high coverage at the manufacturing stage. It delivered targeted IST coverage within the specified time budget and can adapt and scaled with designs in the dynamic automotive market.

Complexity is managed, safety and reliability comprehensively addressed, and the solution delivered on schedule. But to insert something like this requires system-level thinking and test abstraction

Different worlds

Both sides of the ‘new’ automotive market have good reason to work toward raising DFT higher up the flow.

Established automotive IC designers know all about safety and reliability, and that they need to be considered early in a design flow. However, they have historically been less concerned about manufacturing test, because automotive has targeted more mature nodes with more settled design kits. The move toward the bleeding edge fundamentally turning DFT into an RTL issue.

Newcomers to automotive design may have more experience with advanced nodes. But they have historically thought less about safety and reliability in their ‘home’ markets. Targets such as single-digit defects-per-billion and increasingly tough and complex safety standards are also giving them good reason to think about DFT at an earlier stage.

So, not only from the perspectives of design methodology and management but also culturally, the time to move test up the flow has arrived.

Some of Mentor’s work and research in DFT and yield has been collected here.

* “A Hierarchical DFT Architecture for Automotive Designs”, Tal Kogan, Amihay Rabenu, Tal Frucht, and Itay Kroul, Intel; Nilanjan Mukherjee, Mohammed Abdelwahid, and Ron Press, Mentor, 2017 International Workshop on Automotive Reliability and Test (ART).